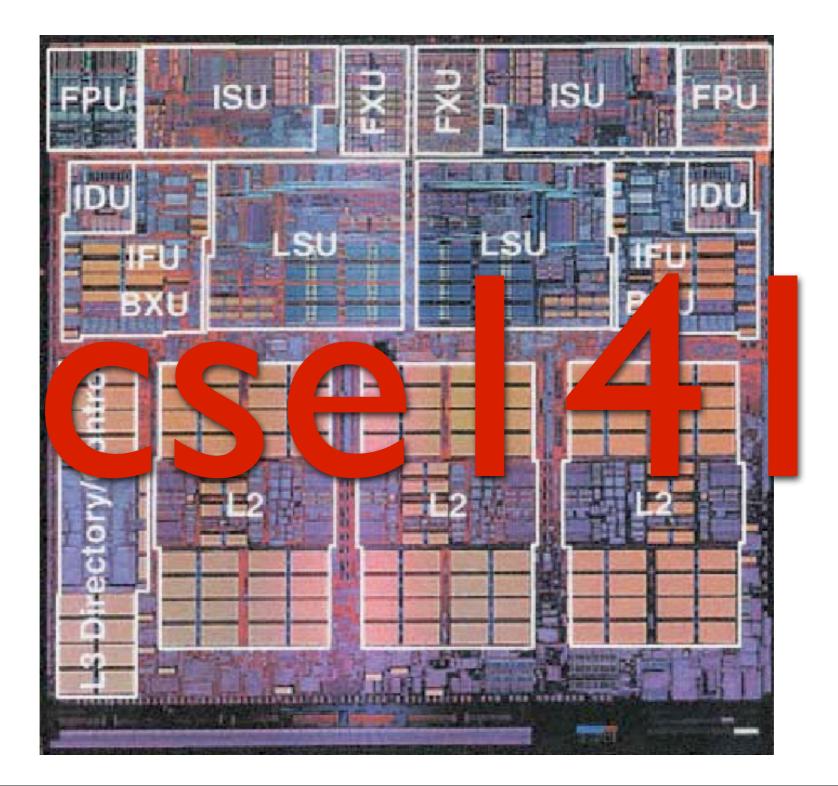

# csel4I: Introduction to Computer Architecture

Steven Swanson Hung-Wei Tseng

# Today's Agenda

- What is architecture?

- Why is it important?

- At the highest level, where is architecture today? Where is it going?

- What's in this class?

## What is architecture?

- How do you build a machine that computes?

- Quickly, safely, cheaply, efficiently, in technology X, for application Y, etc.

Civilization advances by extending the number of important operations which we can perform without thinking about them. -- Alfred North Whitehead

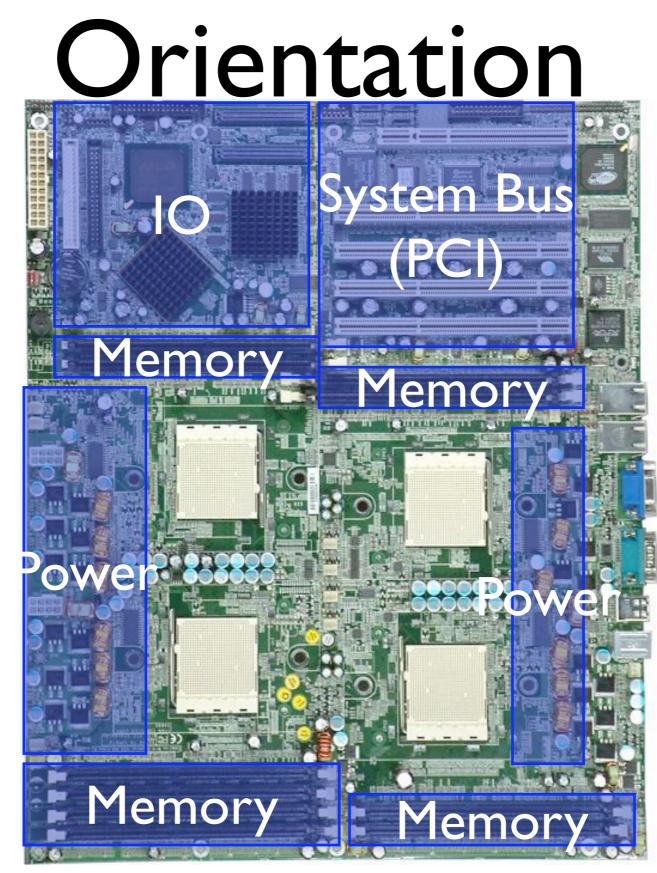

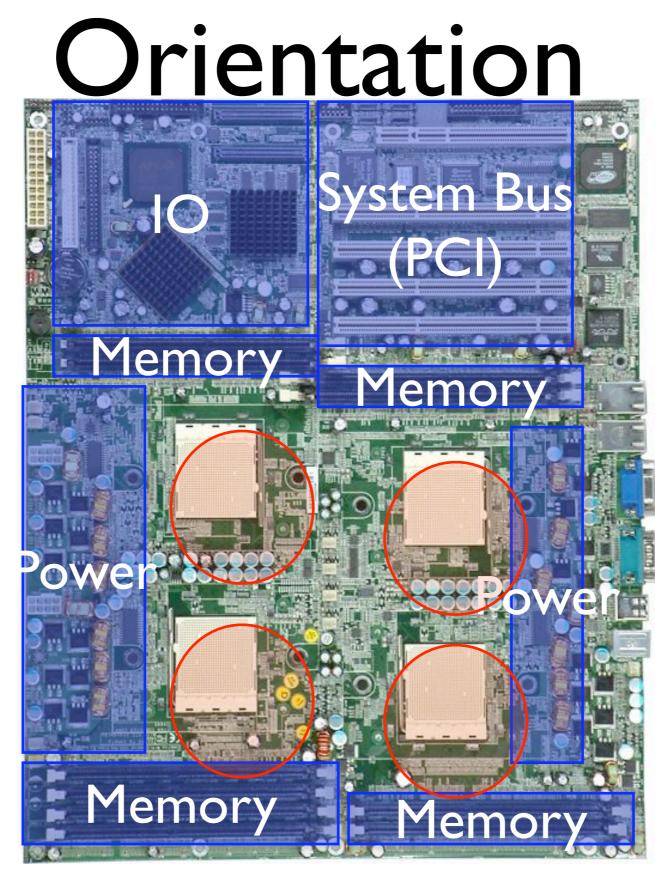

#### Orientation

#### Orientation

#### Architecture begins about here.

#### Architecture begins about here.

### You are here

### You are here

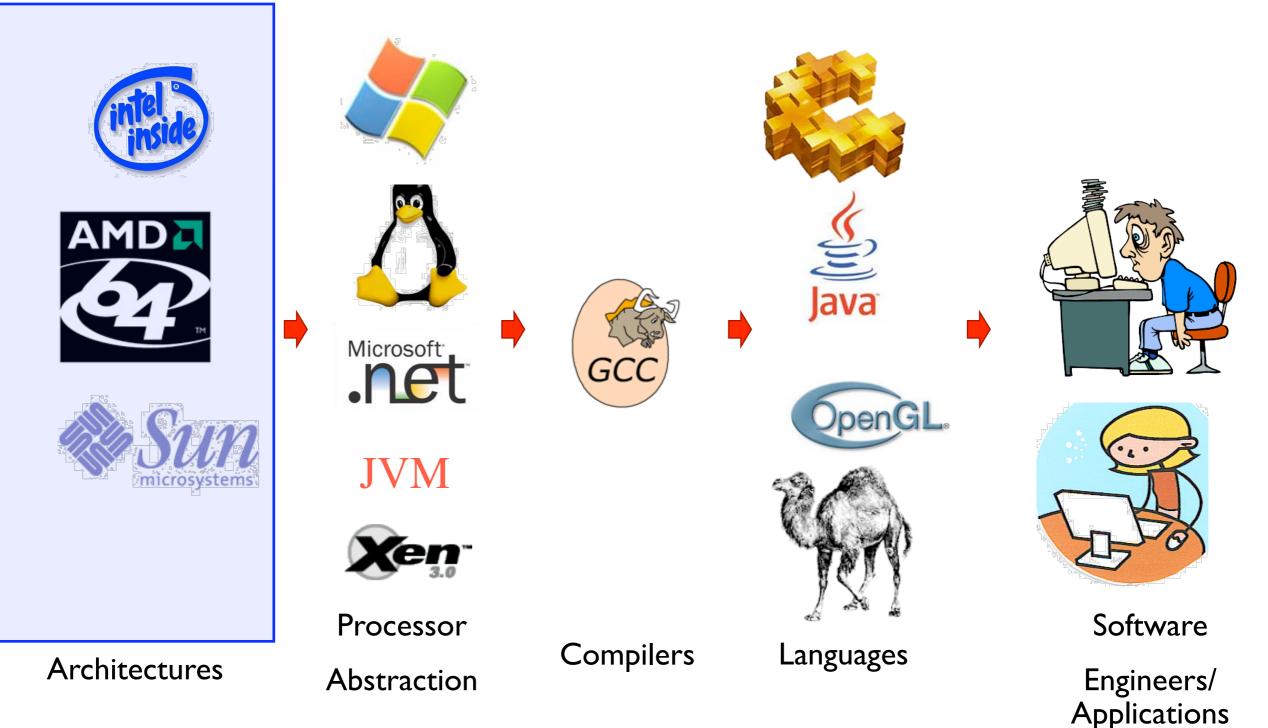

#### The processors go here...

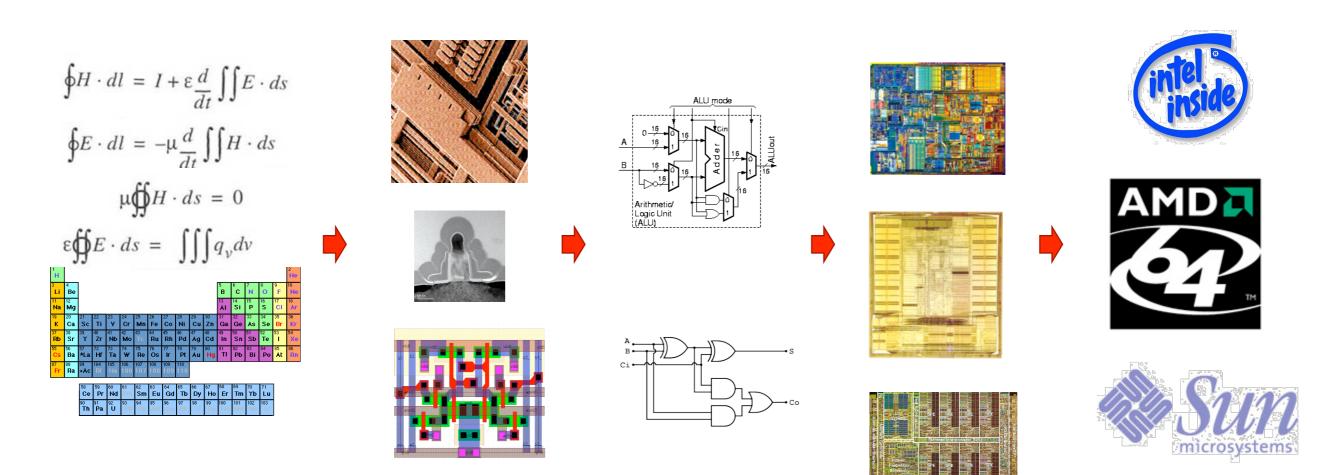

#### Abstractions of the Physical World...

Physics/Materials

Devices

Micro-architecture

Processors

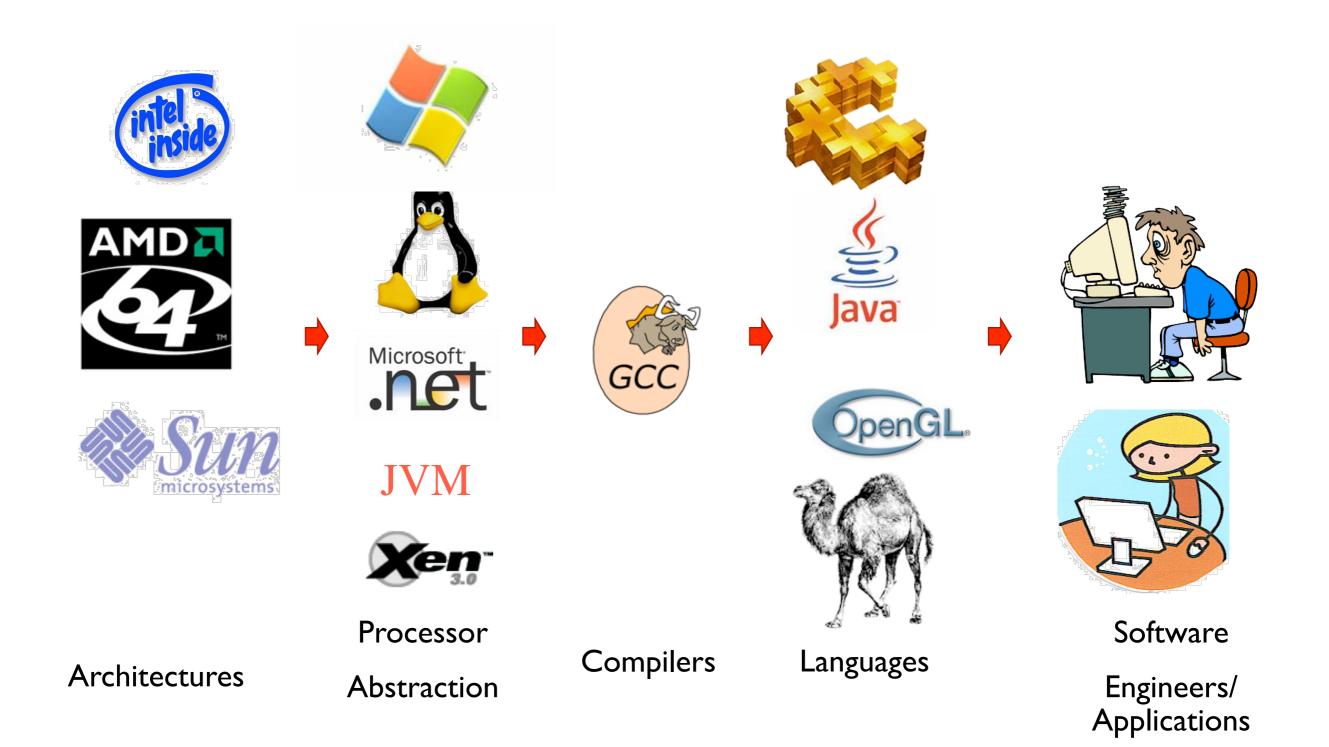

**Architectures**

#### Abstractions of the Physical World...

Physics/ Chemistry/ Material science

$\oint H \cdot dl = I + \varepsilon \frac{d}{dt} \iint E \cdot ds$  $\oint E \cdot dl = -\mu \frac{d}{dt} \iint H \cdot ds$  $\mu \bigoplus H \cdot ds = 0$  $\varepsilon \bigoplus E \cdot ds = \iiint q_{v} dv$

Physics/Materials

Devices

cse241a/

ECE dept

Micro-architecture

This Course

|                                              | and the second se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                              | the second se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                              | ALL - ROUTER CONTRACTOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                              | Contraction of the local division of the loc |

|                                              | And in case of the local division of the loc |

|                                              | Statistical Charge Statistical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                              | and the second s |

|                                              | 10 AP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| _                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                              | ATTS Franking Statements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                              | A DECK DECK DECK DECK DECK DECK DECK DECK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                              | A BAR AND A PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                              | A DOLLAR STOCKED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                              | and the second s |

|                                              | And and the second of the seco |

|                                              | 171 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                              | 72.310-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                              | Summer (1991) - 1992 - Conserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Name of Concession, Name of Street, or other | The second se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                              | And In the Party of the Party o |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### **Processors**

**Architectures**

### ...for the Rest of the System

### ...for the Rest of the System

csel2l csel3l csel30 cseEverythingElse

# Why study architecture?

- As CEs or CSs you should understand how computers work

- Processors are the basis for everything in CS (except theory)

- They are where the rubber meets the road.

- Performance is important

- Faster machines make applications cheaper

- Understanding hardware is essential to understanding how systems behave

- It's cool!

- Microprocessors are among the most sophisticated devices manufactured by people

- How they work (and even that they work) as reliably and as quickly as they do is amazing.

- Architecture is undergoing a revolution

- The future is uncertain

- Opportunities for innovation abound.

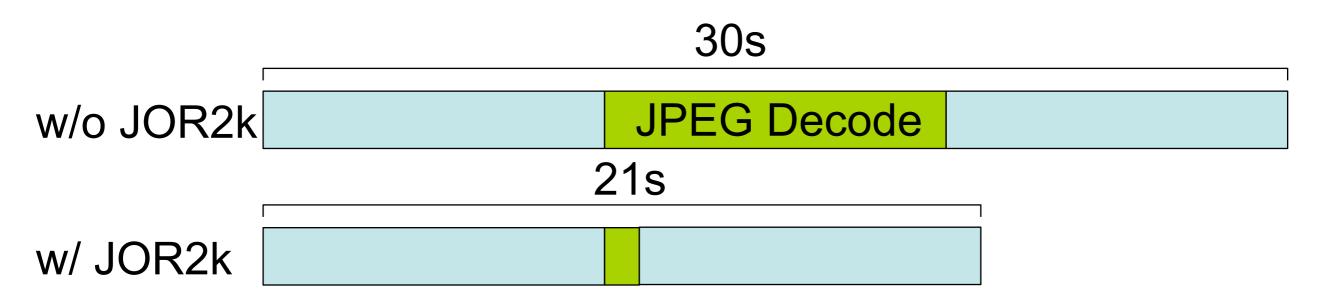

### Performance and You!

• Live Demo

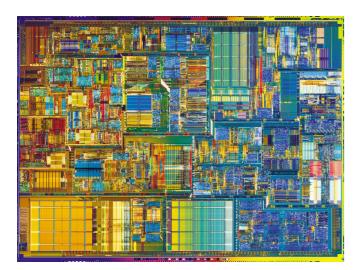

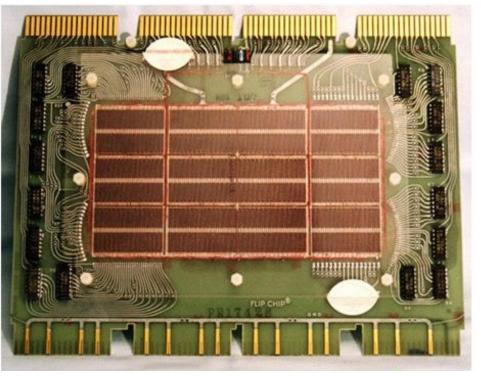

## Processor are Cool!

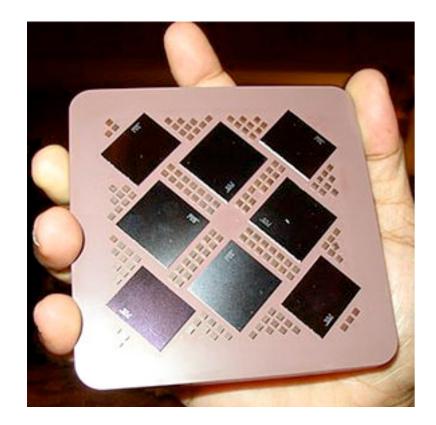

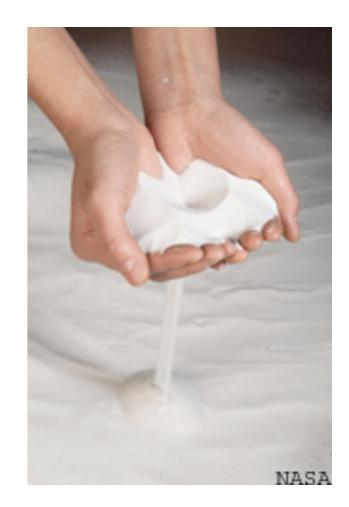

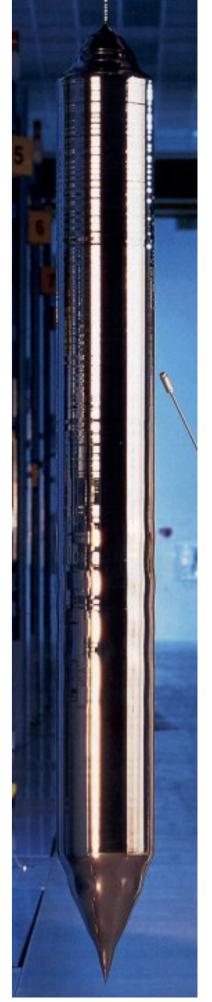

- Chips are made of silicon

- Aka "sand"

- The most adundant element in the earth's crust.

- Extremely pure (<I part per billion)

- This is the purest stuff people make

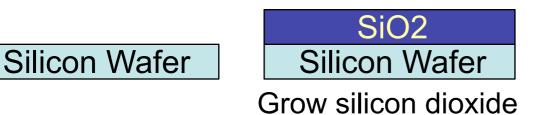

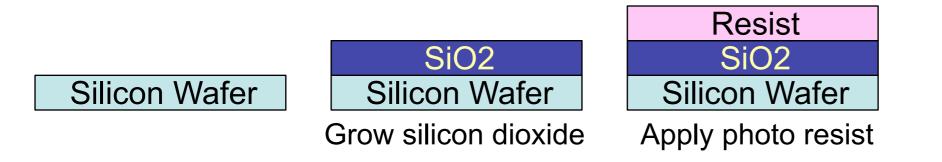

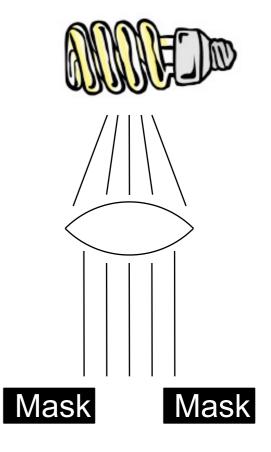

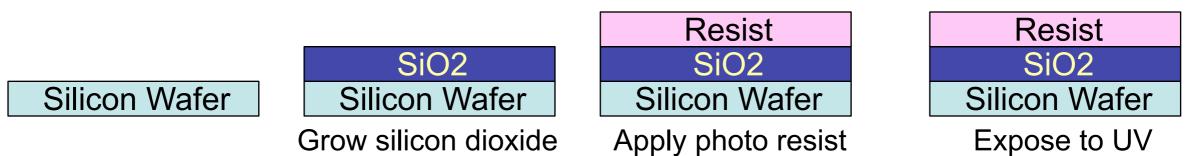

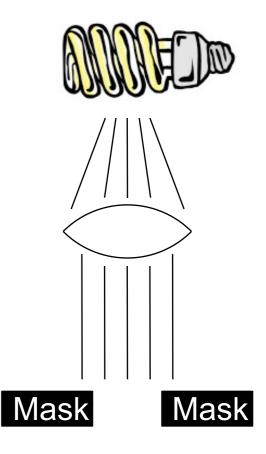

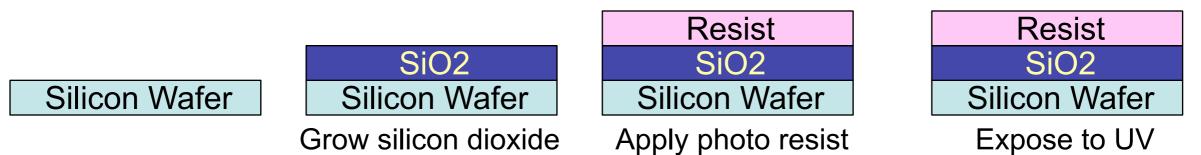

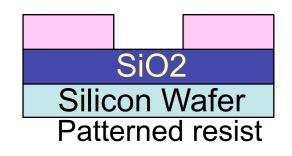

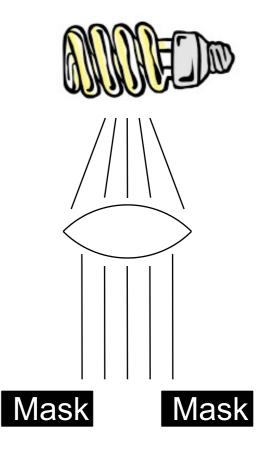

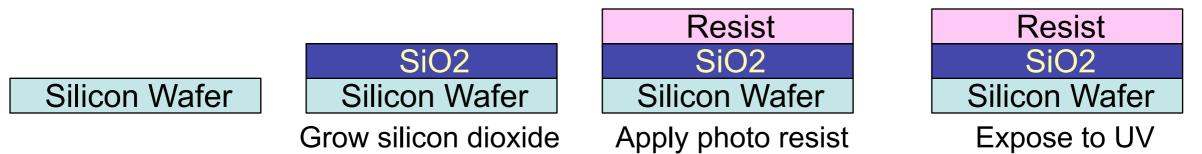

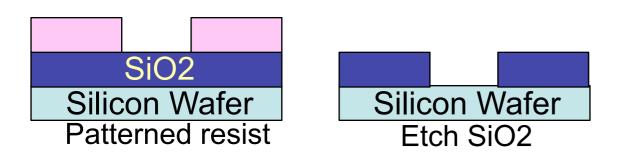

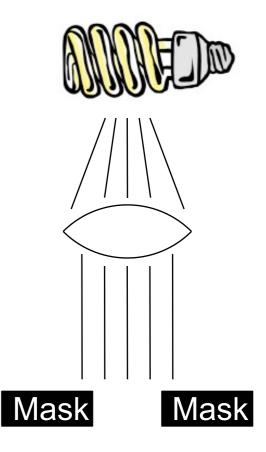

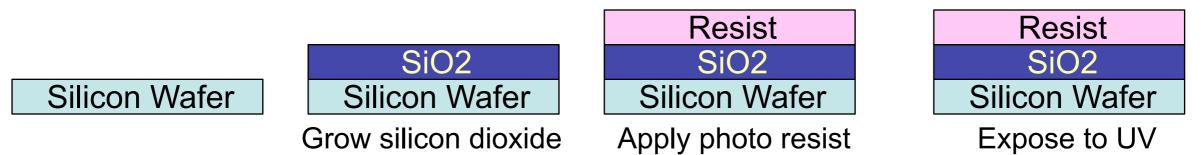

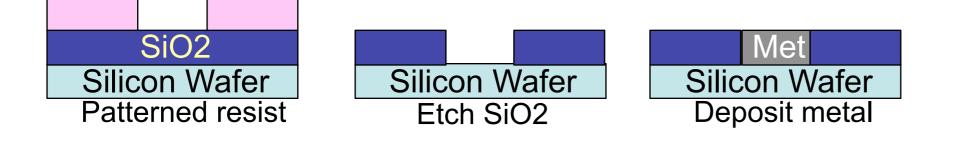

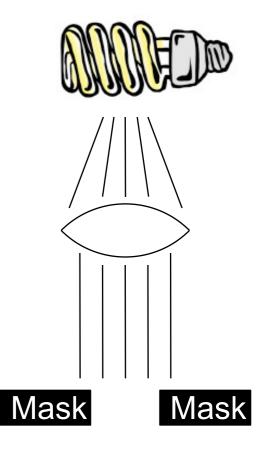

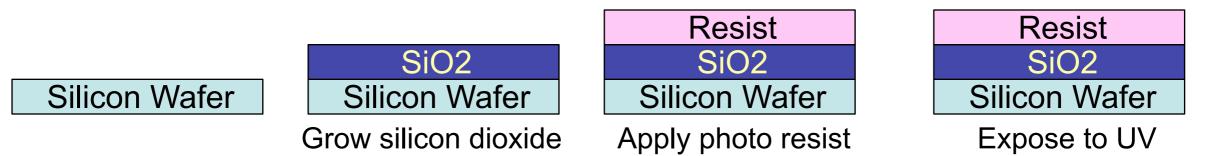

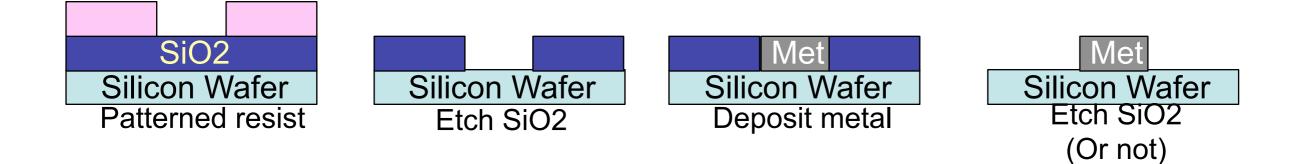

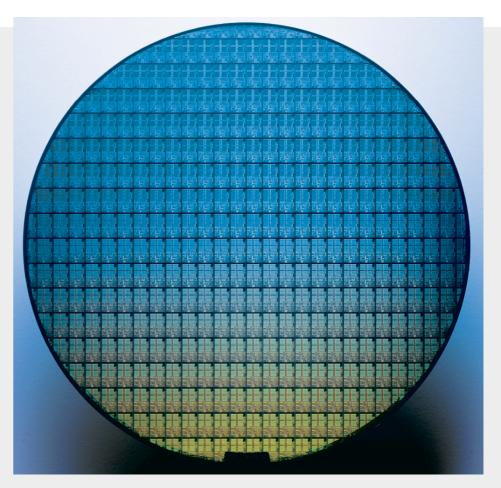

• Photolithography

Silicon Wafer

#### Building Blocks: Transistors

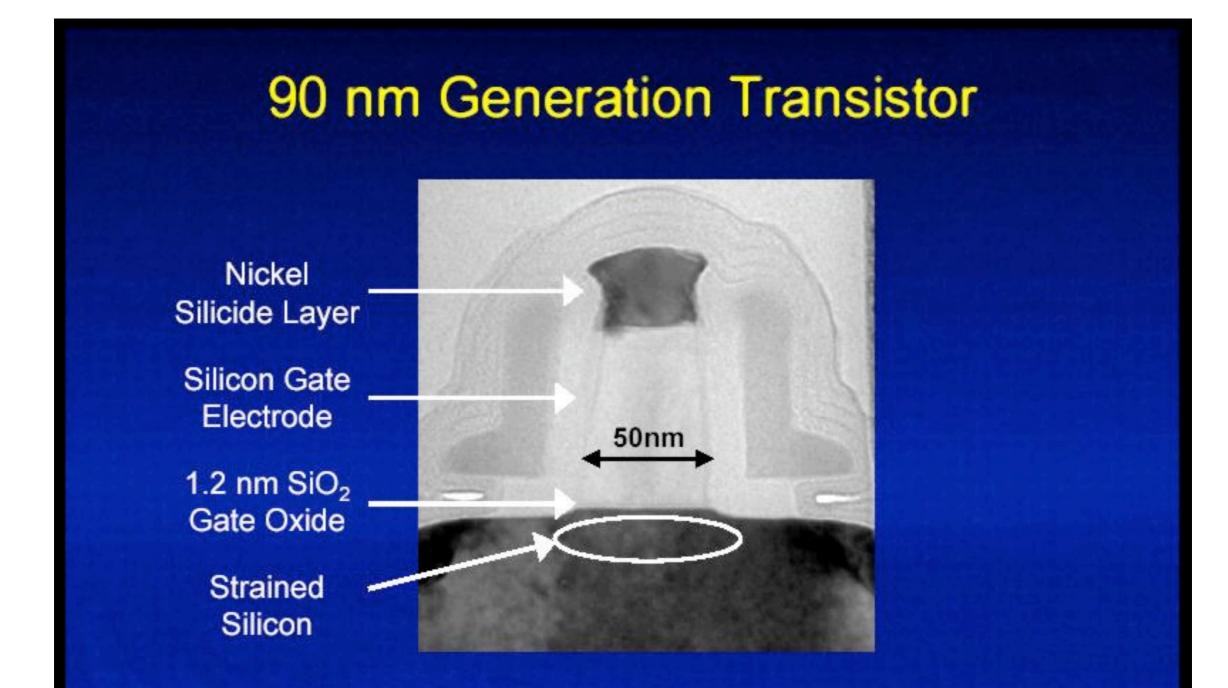

No other company combines these transistor features at the 90 nm generation

#### **Building Blocks:Wires**

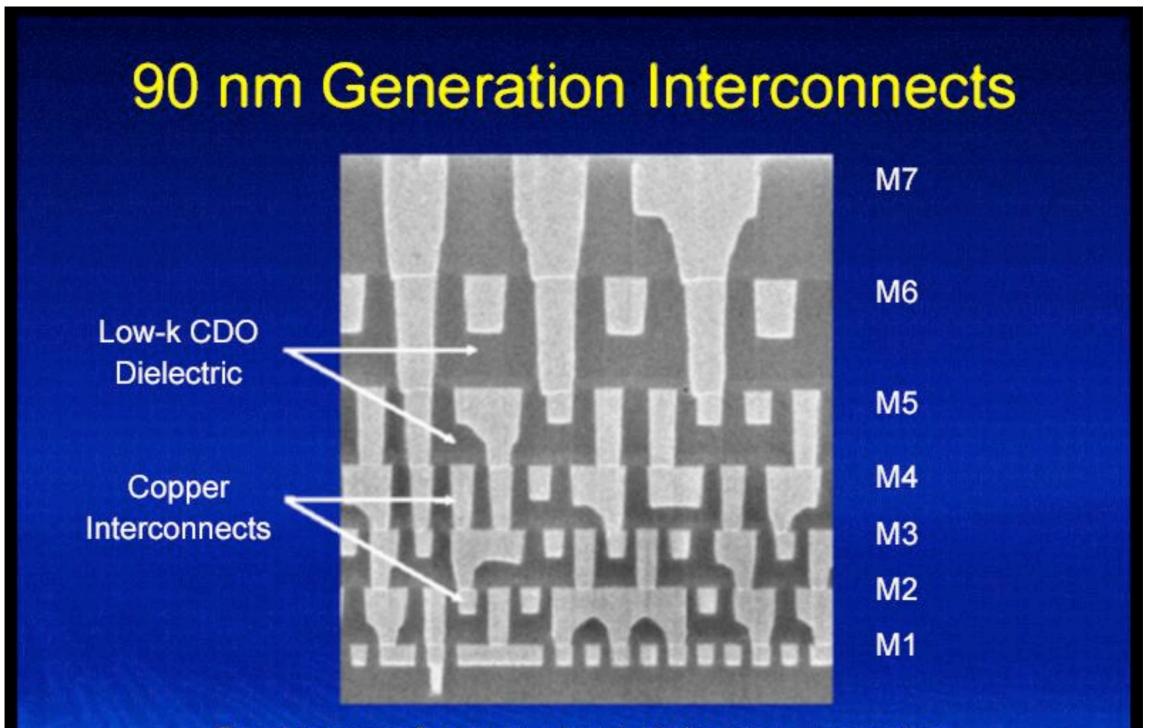

Combination of copper + low-k dielectric now meeting performance and manufacturing goals

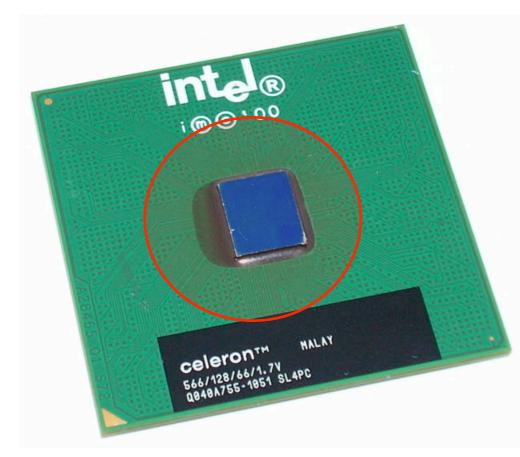

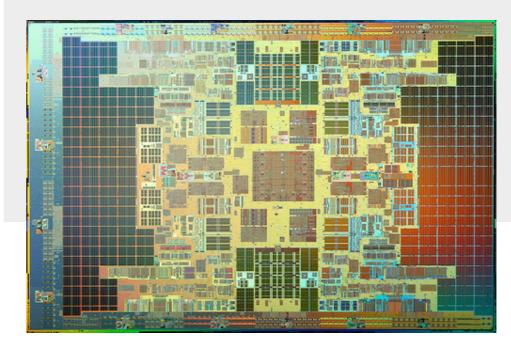

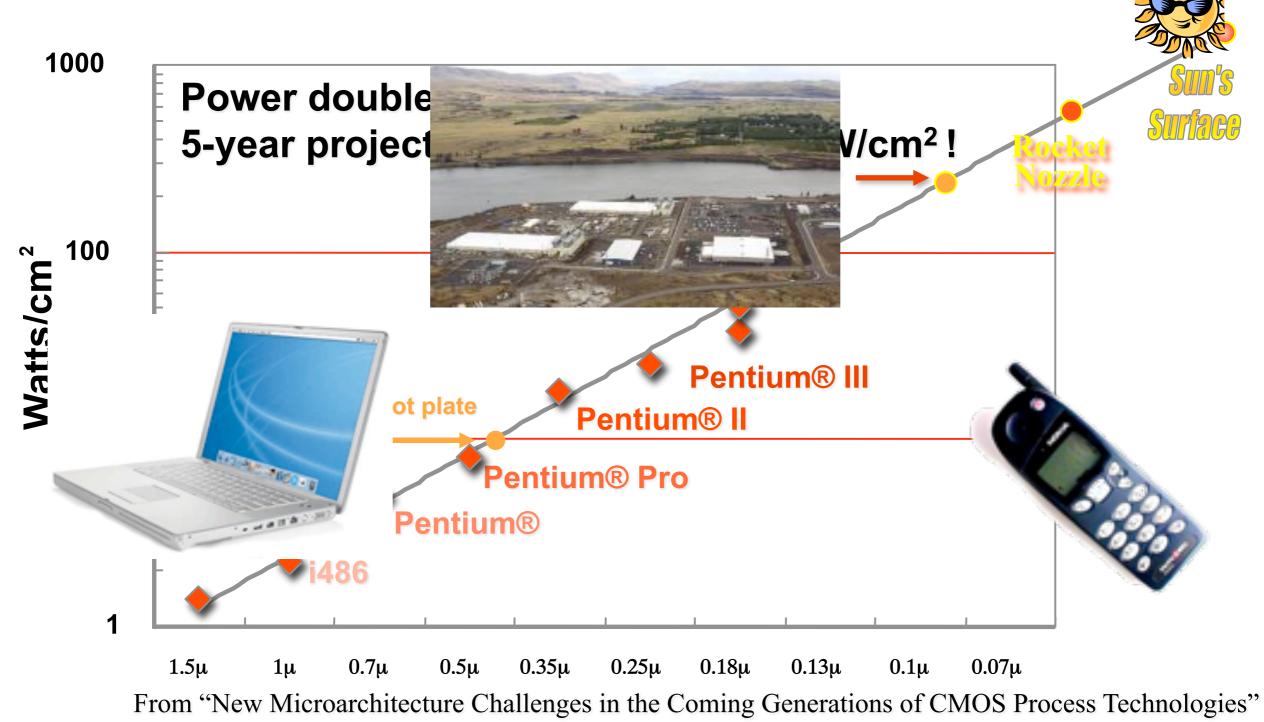

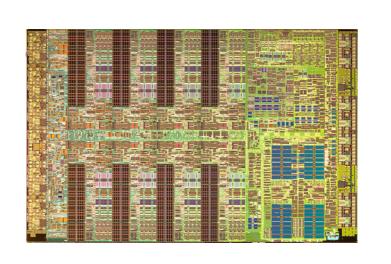

# State of the art CPU

- I-2 Billion xtrs

- 45nm features

- 3-4Ghz

- Several 100 designers

- >5 years

- \$3Billion fab

- 70 GFLOPS

Current state of architecture

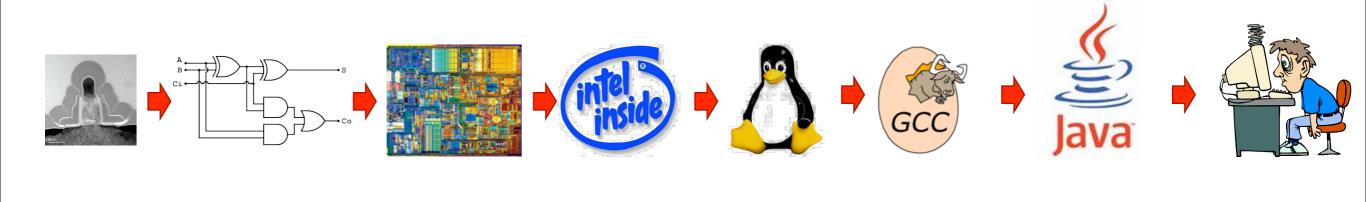

### Since 1940

### Since 1940

- Plug boards -> Java

- Hand assembling -> GCC

- No OS -> Windows Vista

### Since 1940

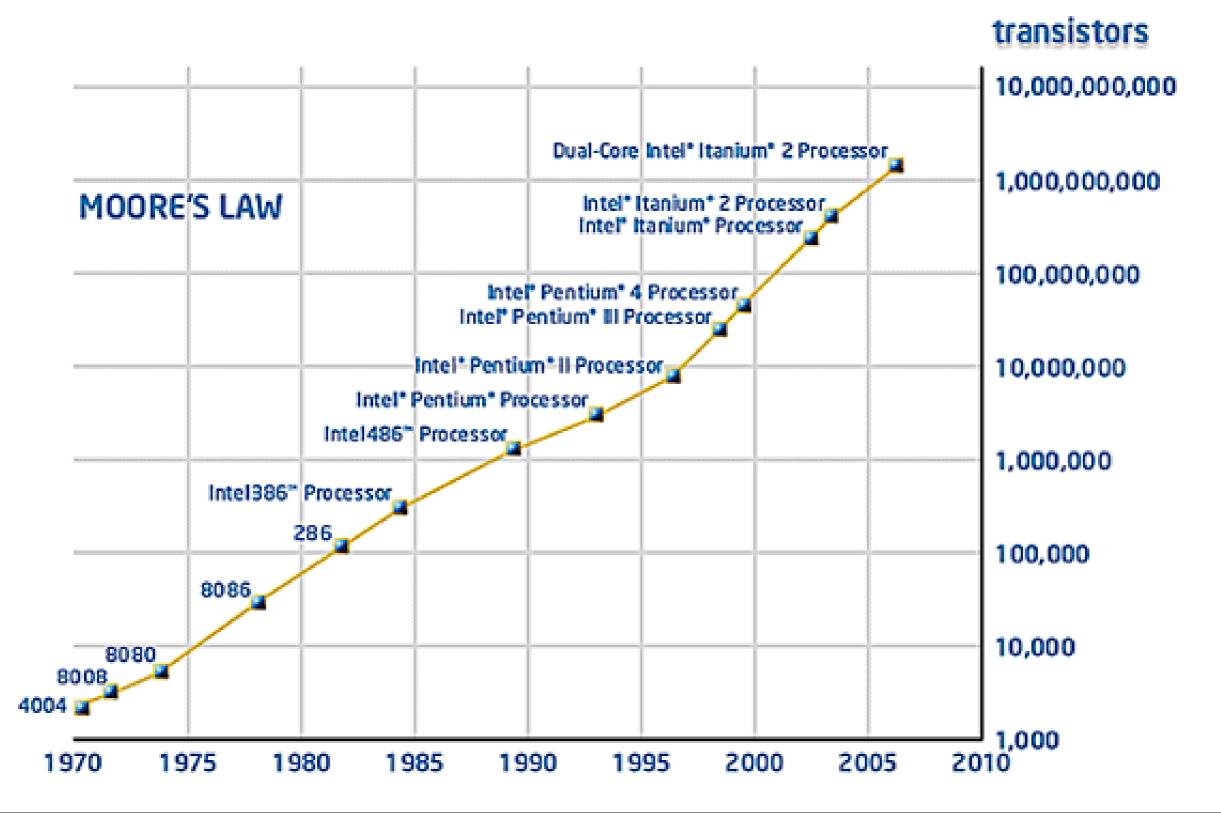

- 50,000 x speedup

- >1,000,000,000 x density (Moore's Law)

- Plug boards -> Java

- Hand assembling -> GCC

- No OS -> Windows Vista

Flexible performance is a liquid asset

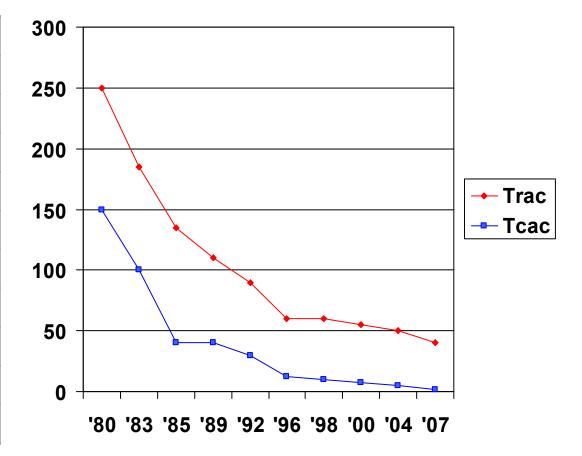

#### Moore's Law: Raw transistors

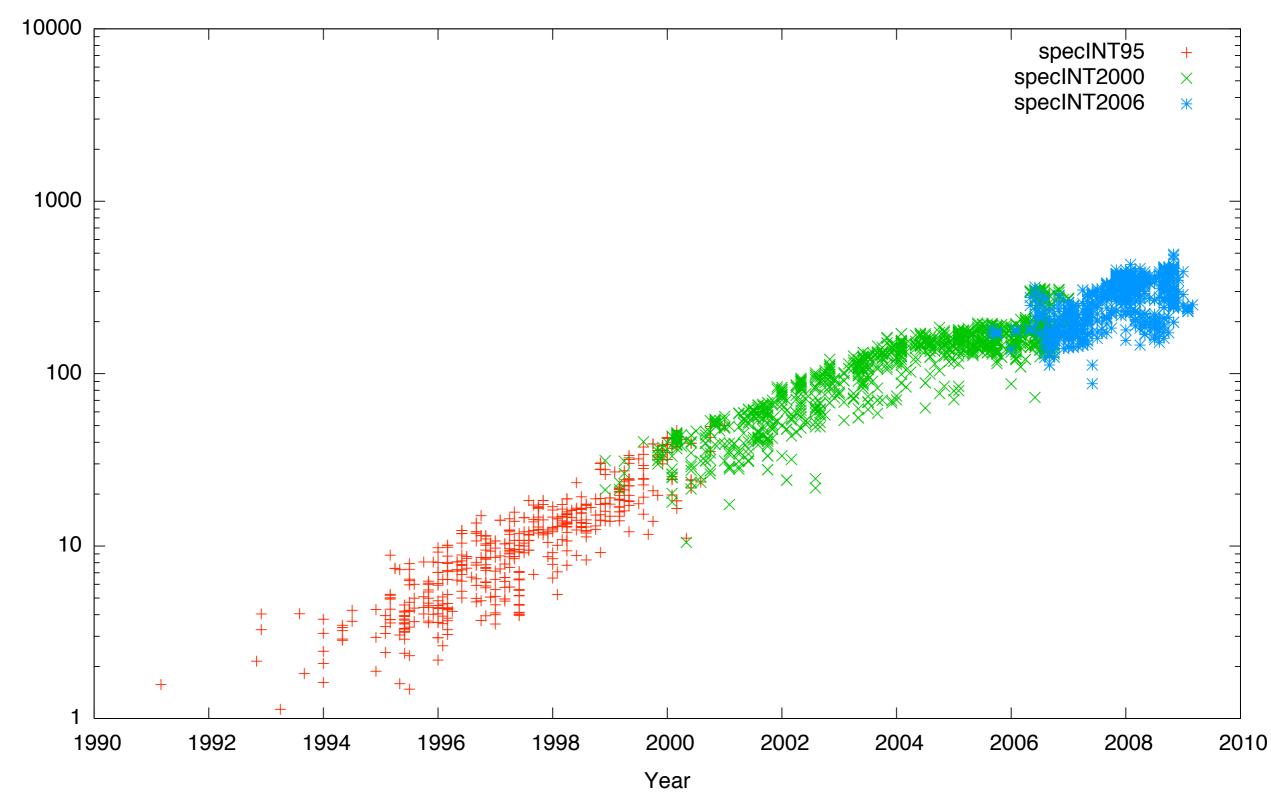

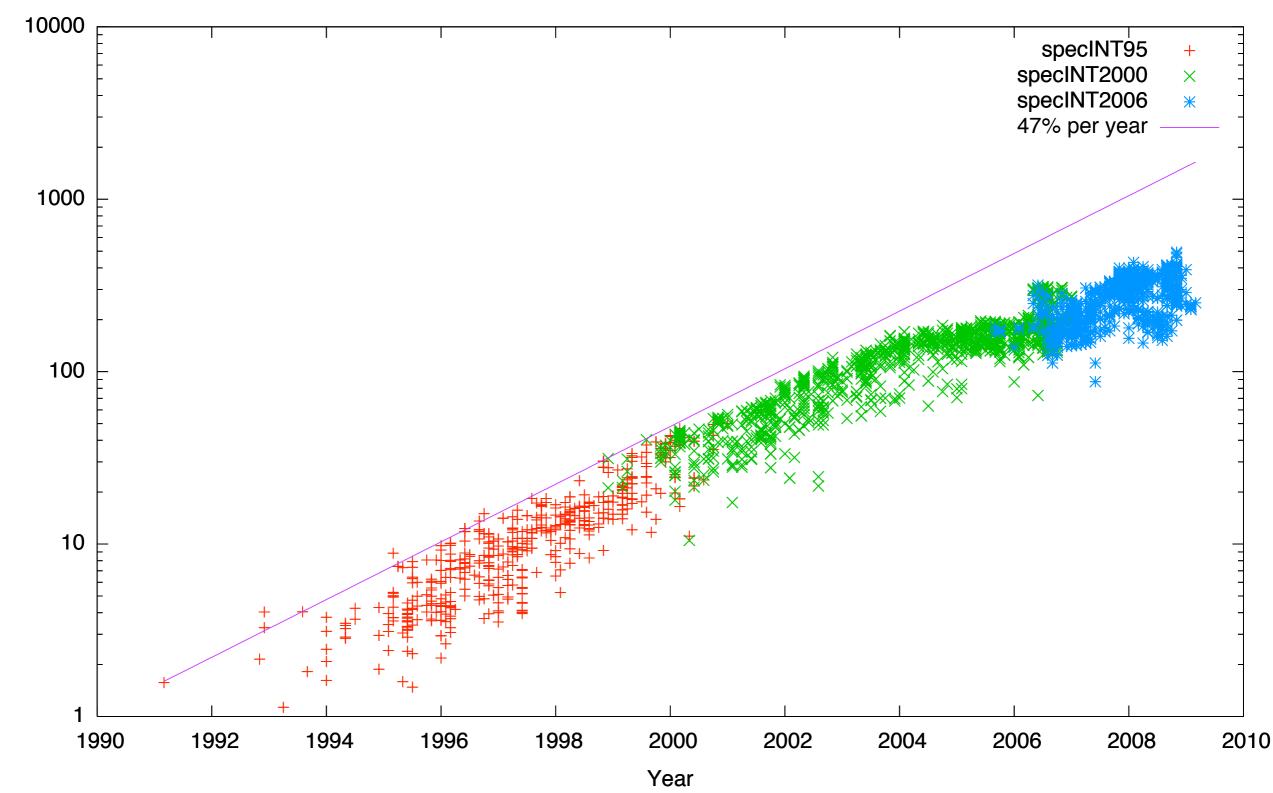

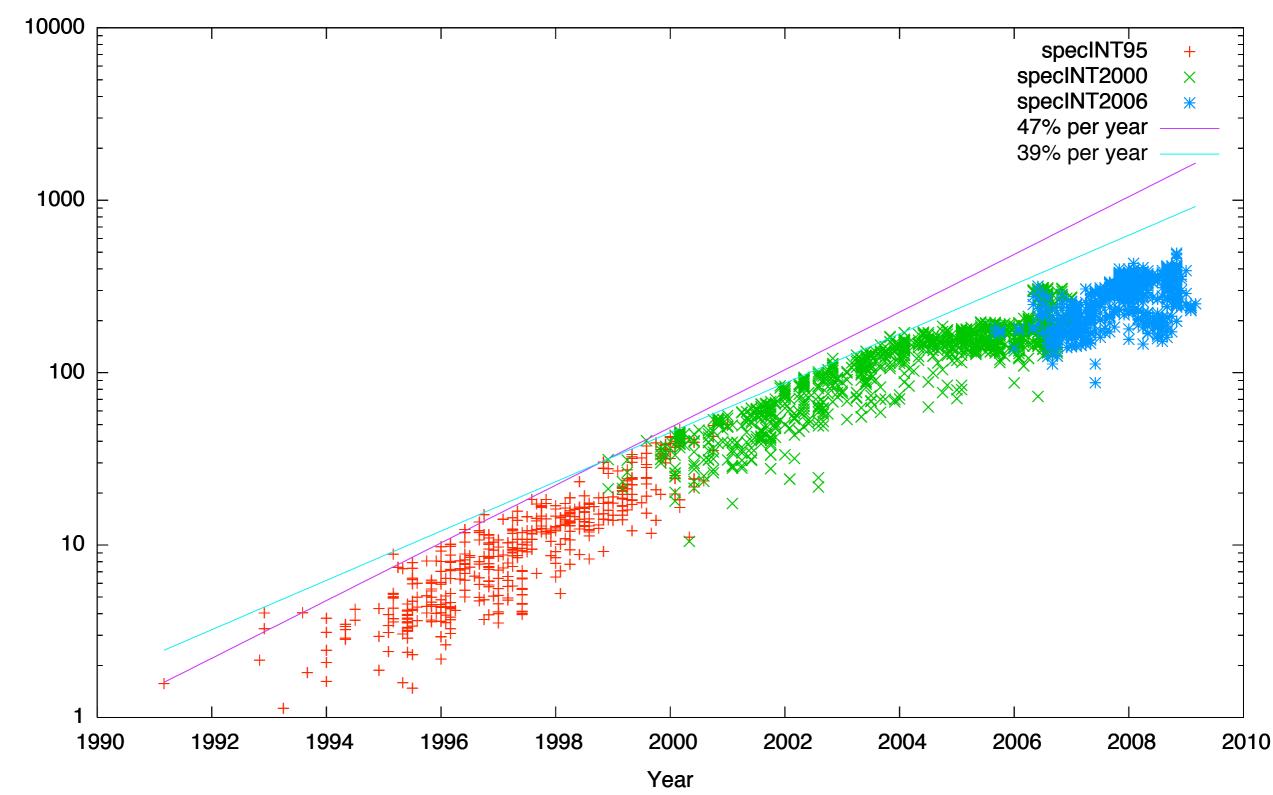

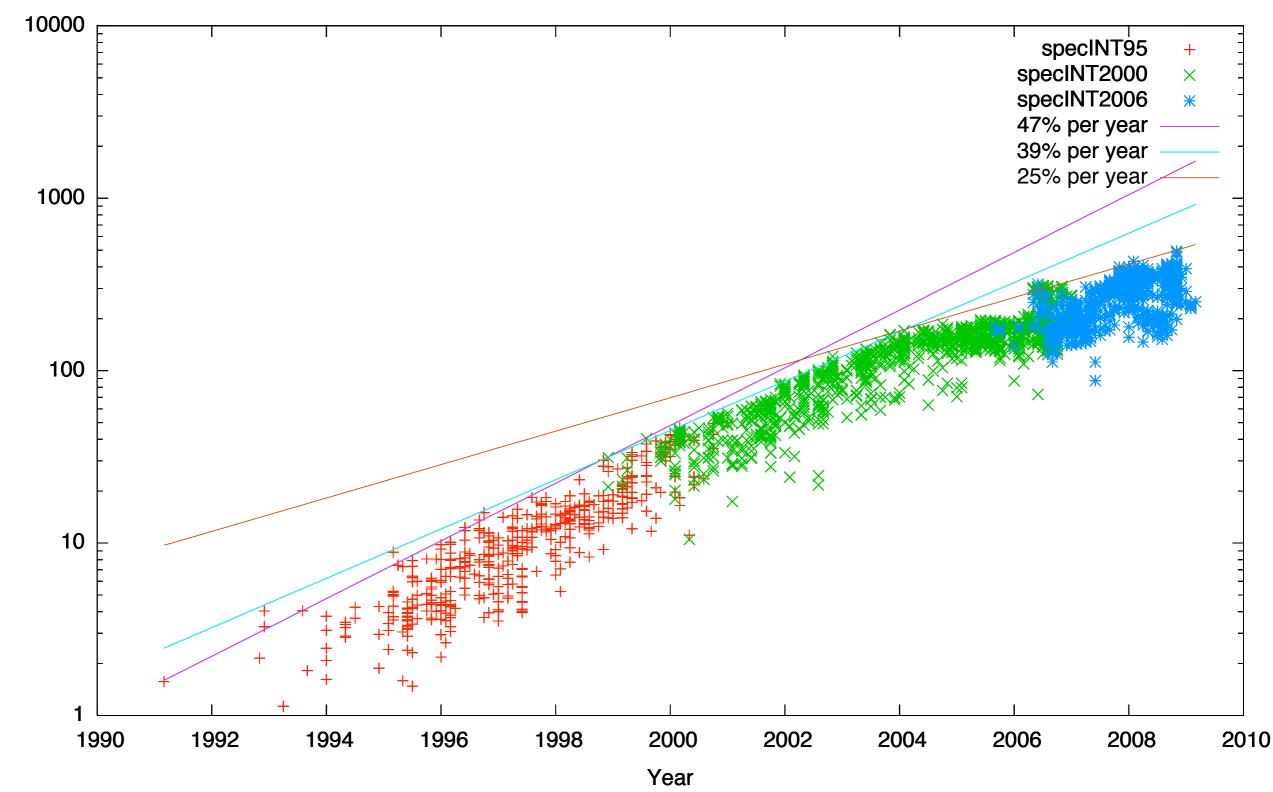

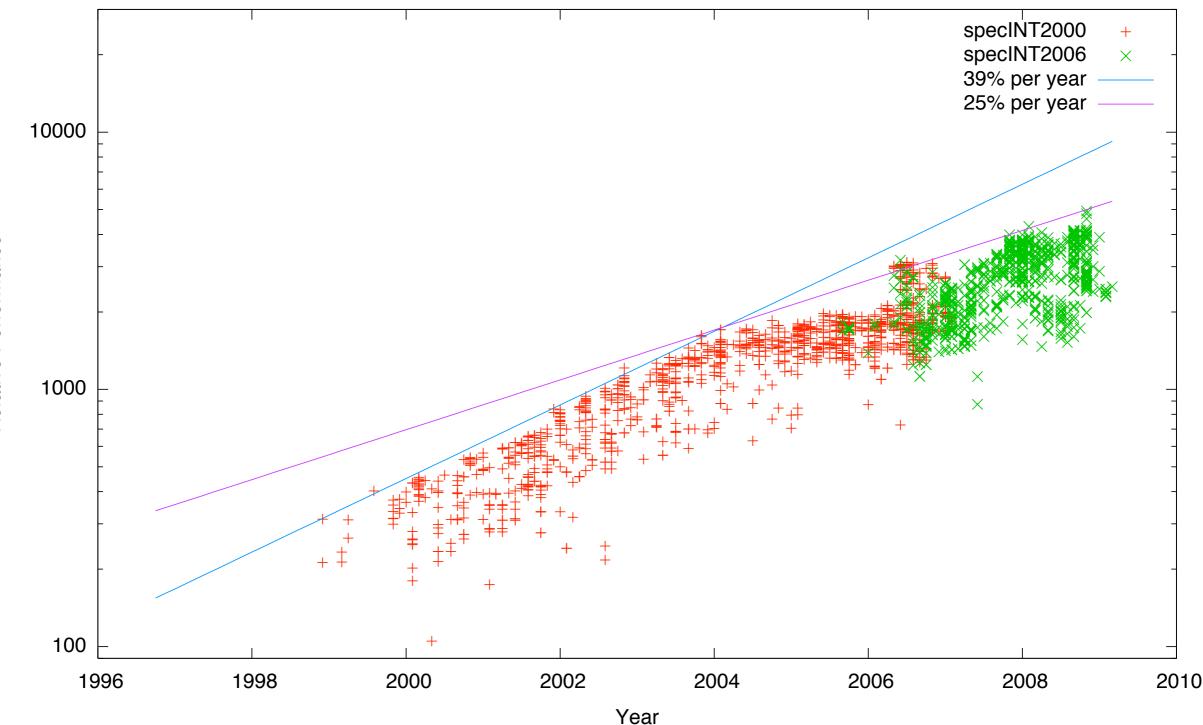

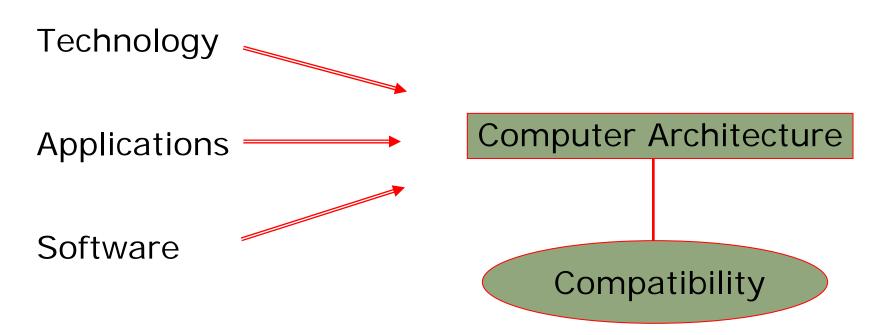

# The Importance of Architecture

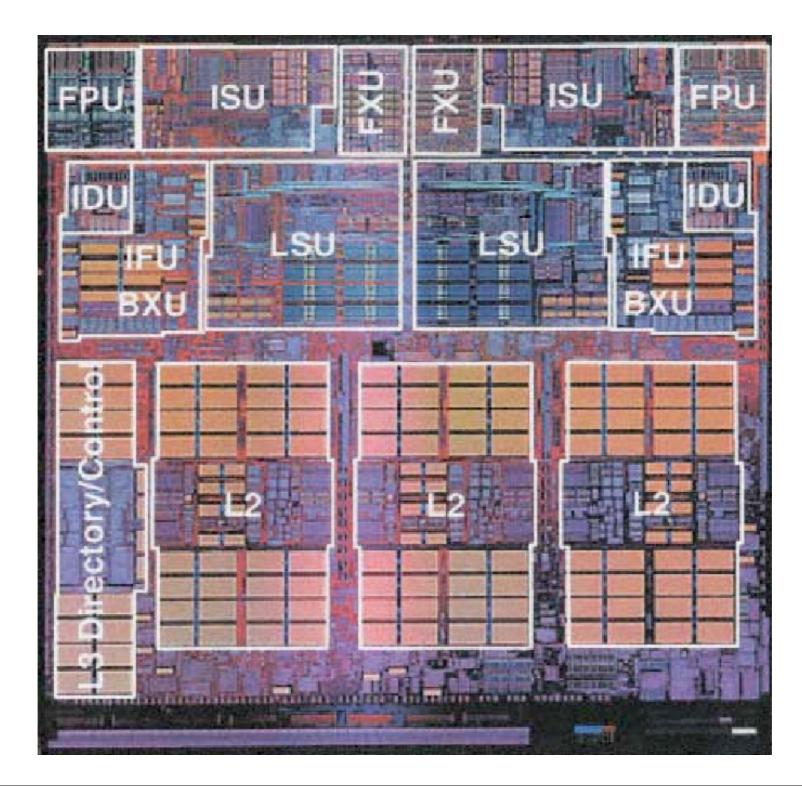

- We design smarter and smarter processors

- Process technology gives us about 20% performance improvement per year

- Until 2004, performance grew at about 40% per year.

- The gap is due to architecture! (and compilers)

**Relative Performance**

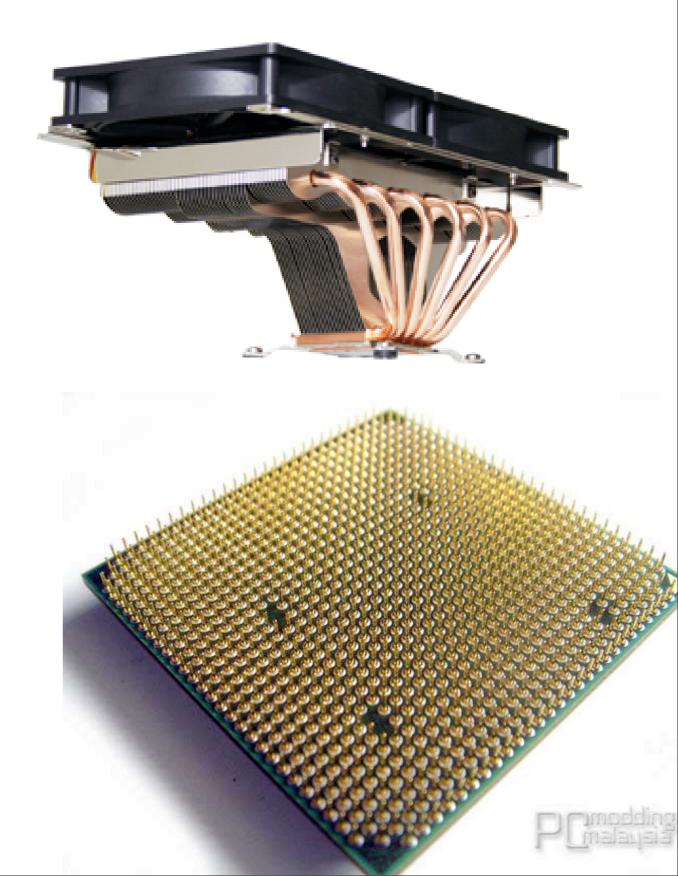

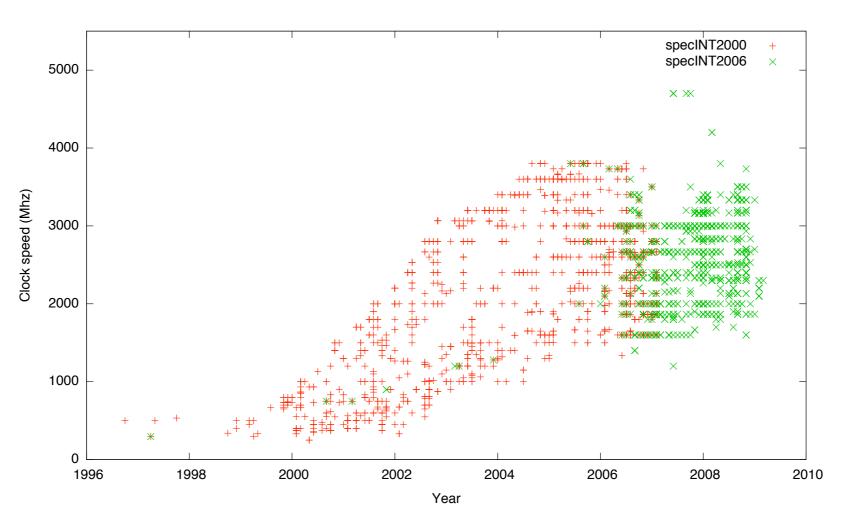

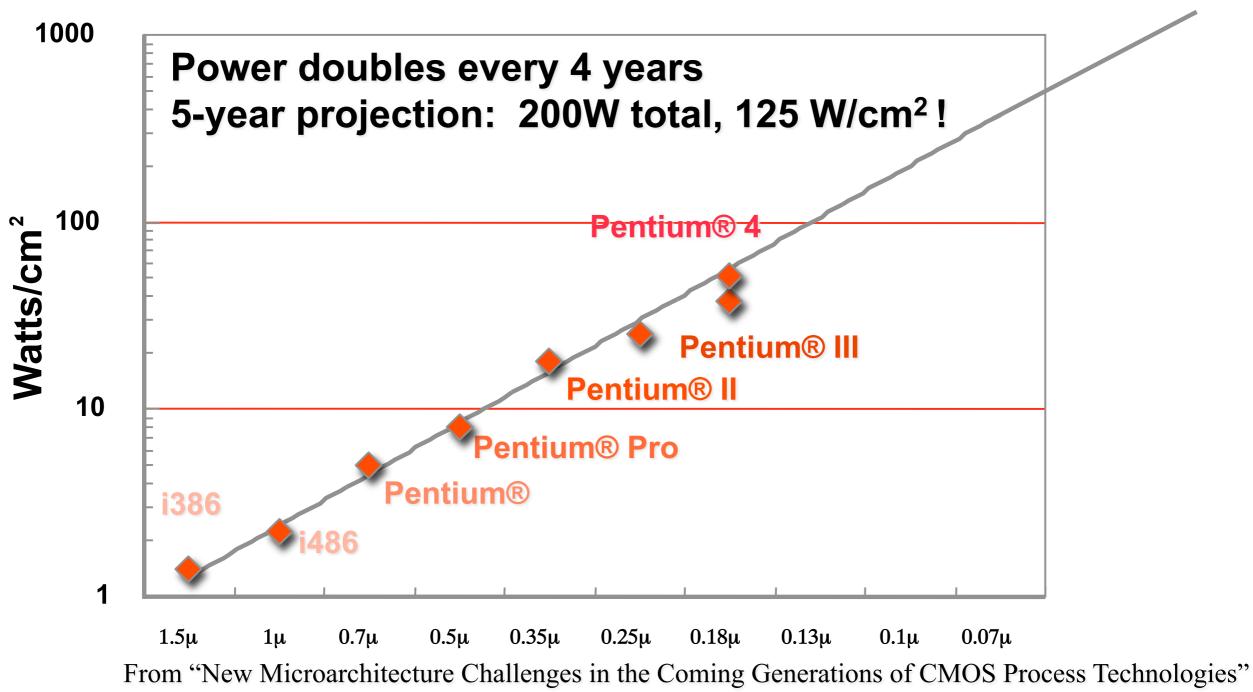

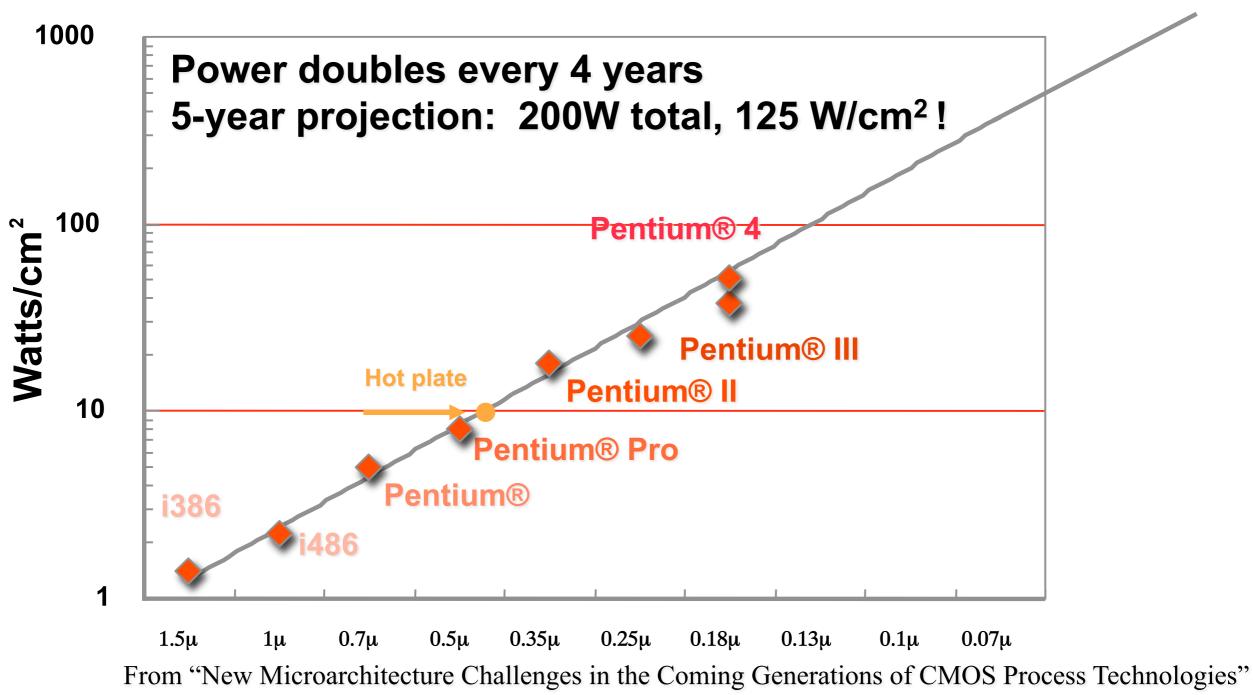

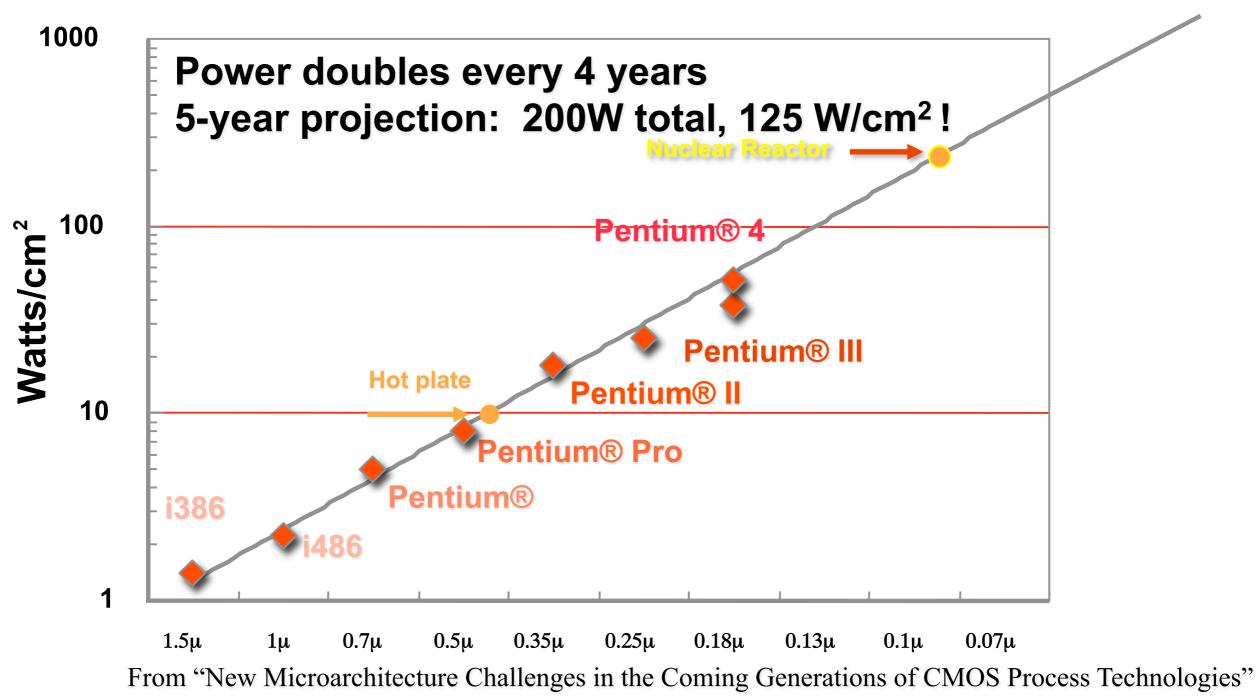

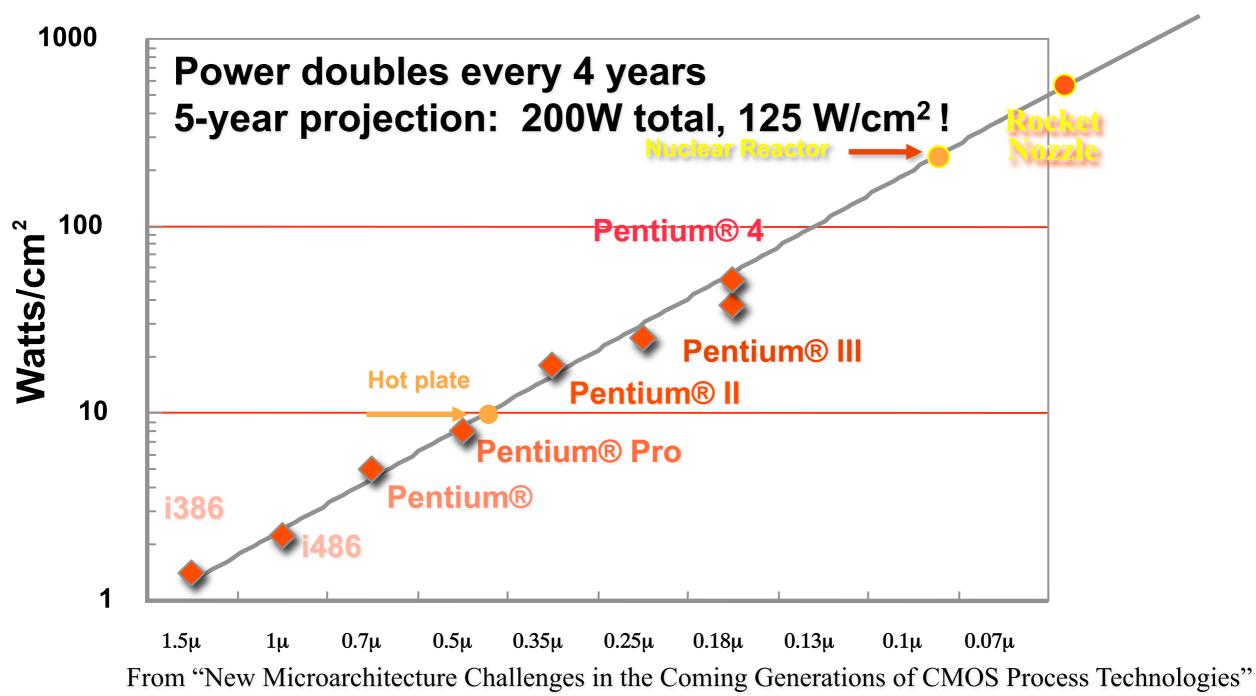

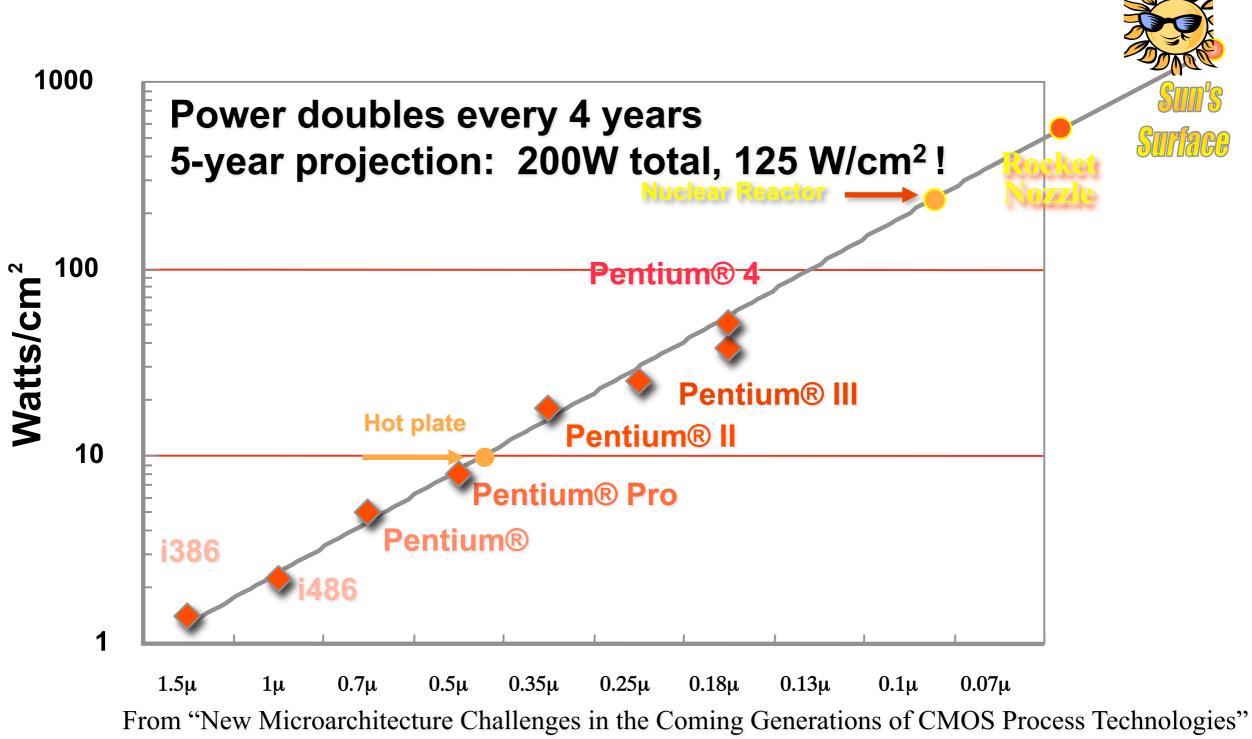

# The clock speed addiction

- Clock speed is the biggest contributor to power

- Chip manufactures (Intel, esp.) pushed clock speeds very hard in the 90s and early 2000s.

- Doubling the clock speed increases power by 2-8x

- Clock speed scaling is essentially finished.

- Fred Pollack, Intel Corp. Micro32 conference key note - 1999.

- Fred Pollack, Intel Corp. Micro32 conference key note - 1999.

#### What's Next: Brainiacs

- Hold the clock rate steady.

- Be smarter in silicon

- More sophisticated processors

- More clever algorithms

- This continues to deliver about 25% per year.

- But for how long?

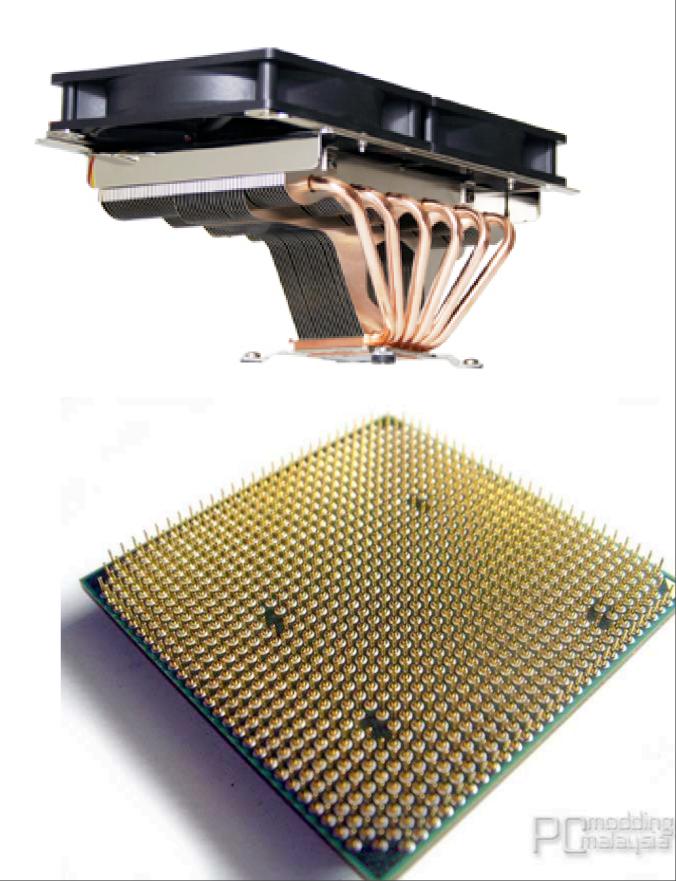

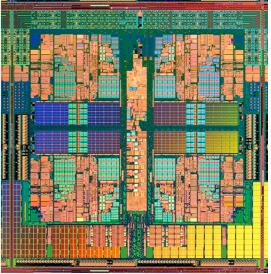

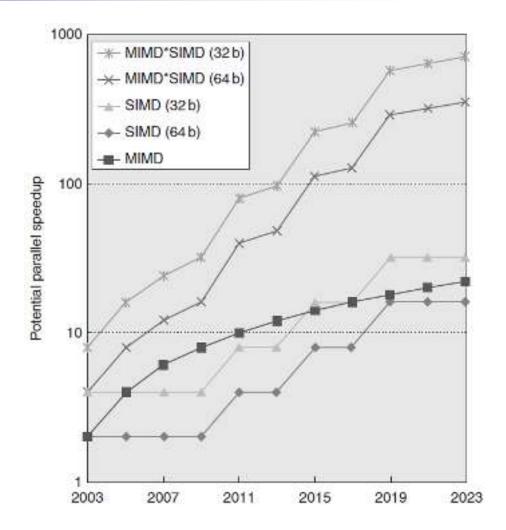

# What's Next: Parallelism

- This is all the rage right now

- You probably own a multi-processor, they used to be pretty exotic.

- They provide some performance, but it's hard to use.

- There aren't that many threads

- Remember, *flexible* performance is a liquid asset

- Remember or look forward to csel21

Intel P4 I core

#### Intel Core 2 Duo 2 cores

#### Intel Nahalem 4 cores

SPARC TI<br/>8 coresIntel PrototypeCell BEAMD Barcelona8 cores80 cores8 + 1 cores4 cores

**Relative Performance**

29

#### Course Staff

- Instructor: Steven Swanson

Lectures Tues + Thurs

- TA: Hung-Wei Tseng

- Discussion sec:Wed.

- (but not this week)

• See the <u>course web page</u> for contact information and office hours.

### What's in this Class

#### • Course outline

- Instruction sets

- The basics of silicon technology

- Measuring performance

- How processors work

- Basic pipelining

- Data and control hazards

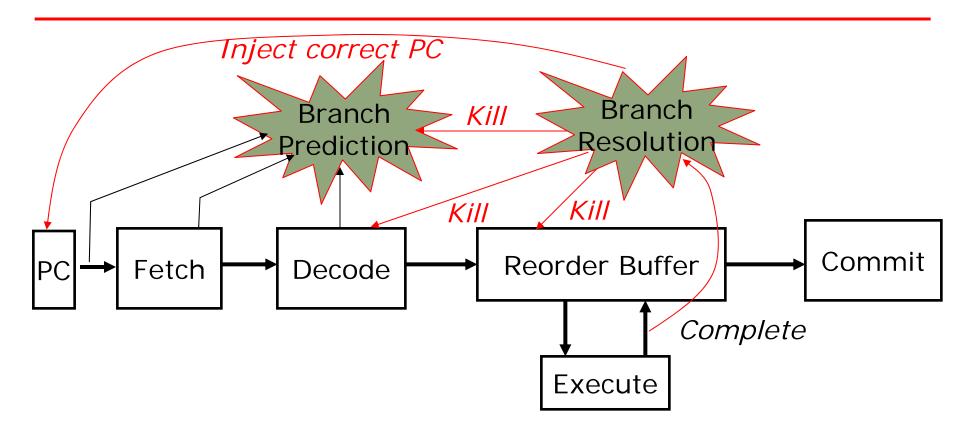

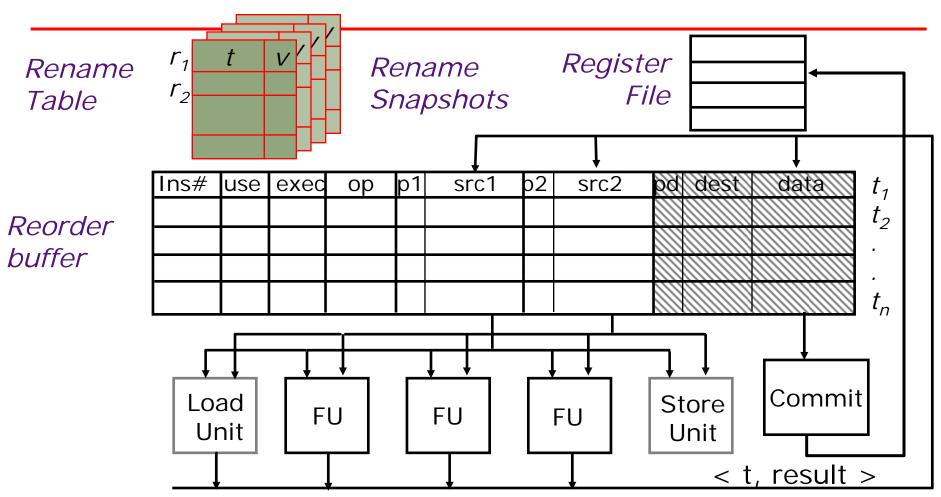

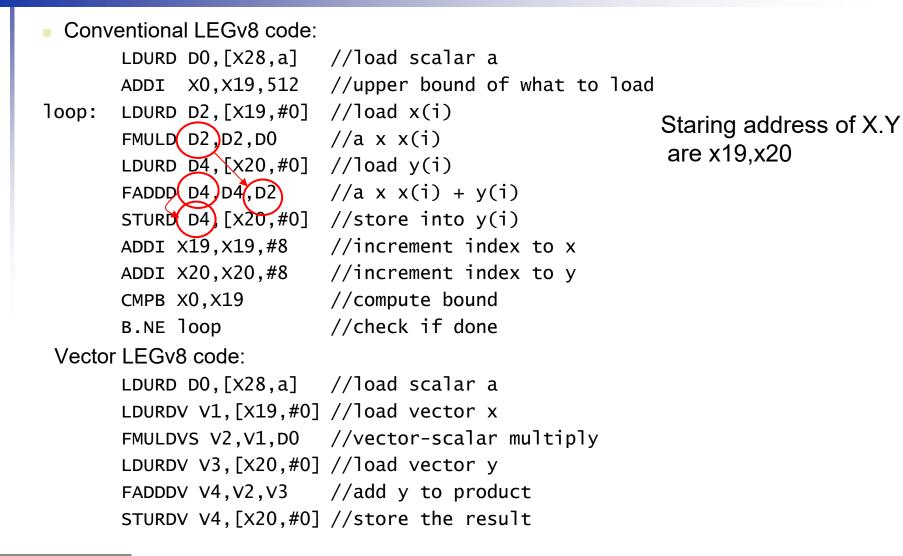

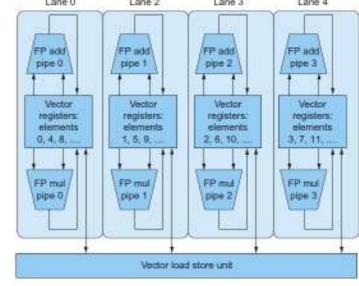

- Branch prediction and speculation

- The memory system

- Introduction to multiprocessors

- Weekly technology digressions

- How various technologies actually work.

### Your Tasks

- Read the text!

- Computer Organization and Design: The Hardware/Software Interface (4th Edition) -- previous editions are not supported

- I'm not going to cover everything in class, but you are responsible for all the assigned text.

- Come to class!

- I will cover things not in the book. You are responsible for that too.

- Class participation (5%)

- Homeworks throughout the course. (10%)

- Weekly quizzes on Thursdays (10%)

- One midterm. (25%)

- One cumulative final. (35%)

- One project (15%)

- Design your own ISA!

### The Link to 141L

- You do not need to take 141L along with 141, but you may need both to get your degree.

- The classes are mostly independent, except

- The results of the project will be used in I4IL

- You can earn extra credit by licensing your ISA groups in 141L who are not in 141

# Grading

- Grading is on a 13 point scale -- F through A+

- You will get a letter grade on each assignment

- Your final grade is the weighted average of the assignment grades.

- An excel spreadsheet calculates your grades

- We will post a sanitized version online once a week.

- It will tell you exactly where you stand.

- It specifies the curves used for each assignment etc.

- OpenOffice doesn't run it properly.

### Academic Honesty

#### • Don't cheat.

- Cheating on a test will get you an F in the class and no option to drop, and a visit with your college dean.

- Cheating on homeworks means you don't have to turn them in any more, but you don't get points either. You will also take at least 25% penalty on the exam grades.

- Copying solutions of the internet or a solutions manual is cheating.

- Review the UCSD student handbook

- When in doubt, ask. Honest mistakes will be forgiven.

#### CpE 252 Computer Organization & Design

#### **Central Processing Unit**

#### **Central Processing Unit (CPU)**

- Introduction

- General Register Organization

- Stack Organization

- Instruction Formats

- Addressing Modes

- Data Transfer and Manipulation

- Program Control

- Reduced Instruction Set Computer

- Datapath

- Storage Components; Registers & Flags

- Processing Components; Arithmetic, Logic, Shift Unit (ALSU)

- Transfer Components; Bus

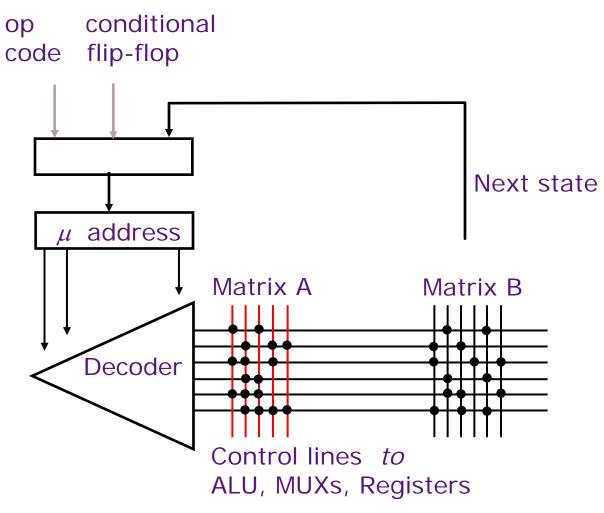

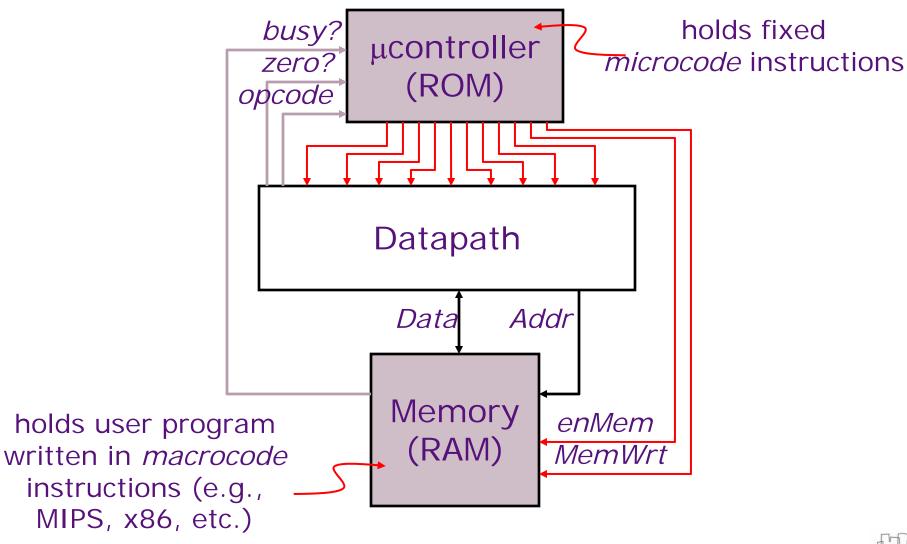

- Control

- Control Unit

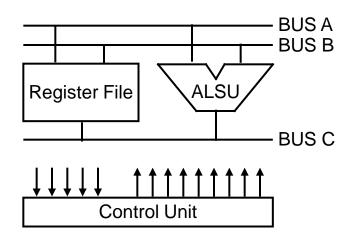

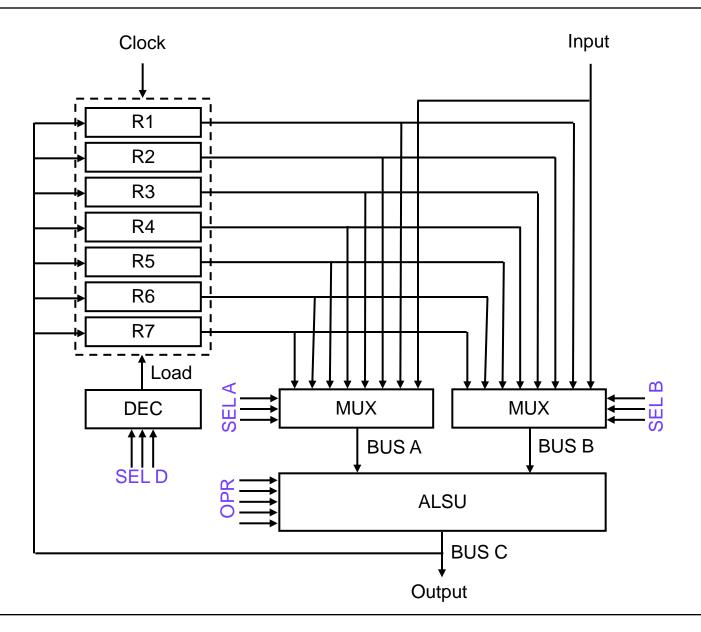

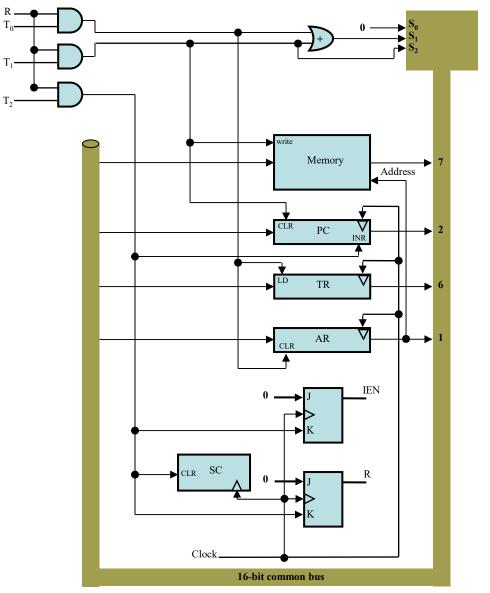

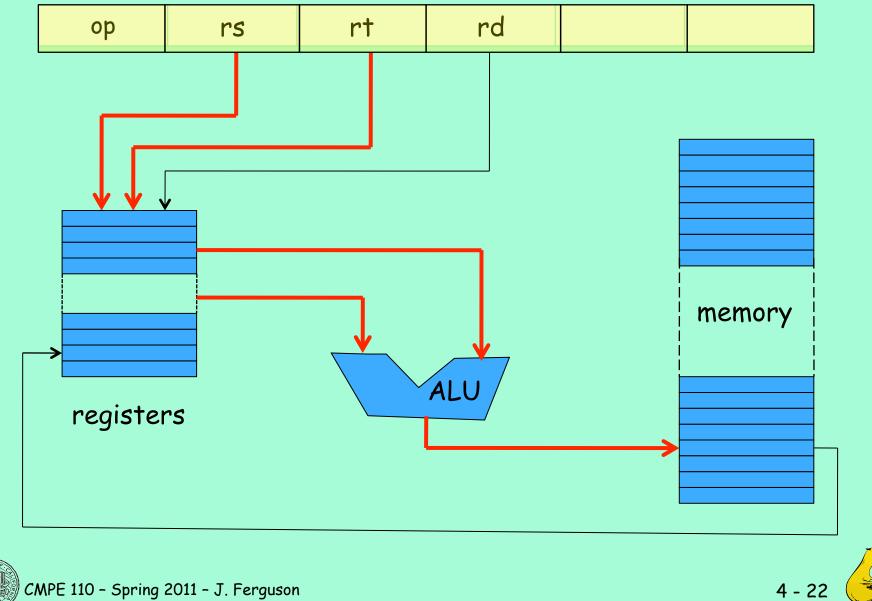

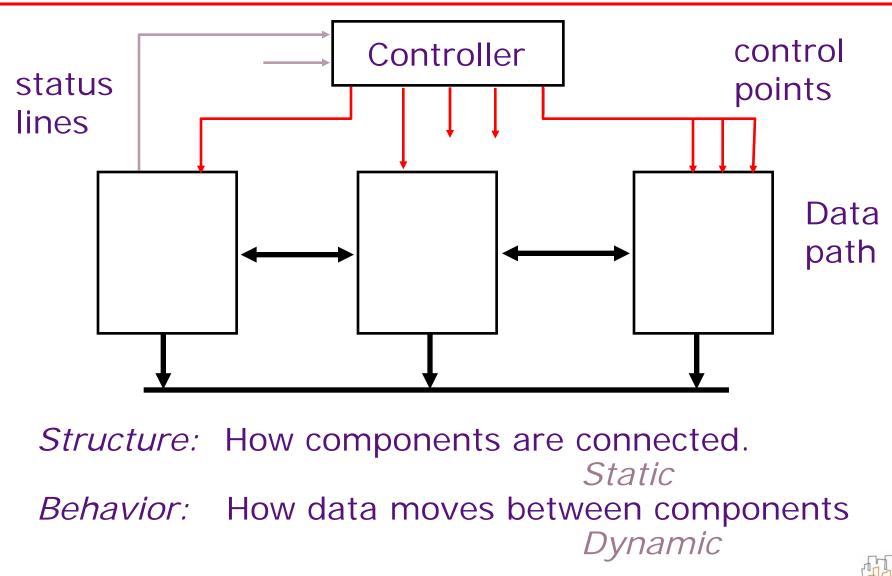

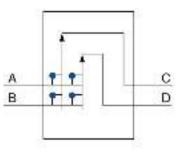

#### General Register Organization - Datapath

#### **Operation of Control Unit**

- Control Unit, directs the information flow through ALU by

- Selecting various Components in the system

- Selecting the Function of ALU

- □ Example:  $R1 \leftarrow R2 + R3$

- ↔ SELA: BUS A ← R2

- $\leftarrow$  SELB: BUS B ← R3

- OPR: ALU instruction to ADD

- ♦ SELD: R1 ← BUS C

| 3 bits | 3 bits | 3 bits     | 5 bits |

|--------|--------|------------|--------|

| SELA   | SEL B  | SEL D      | OPR    |

|        | Cor    | ntrol Word |        |

| Field Encoding<br>Binary Code | SELA  | SELB  | SELD |

|-------------------------------|-------|-------|------|

| 000                           | Input | Input | None |

| 001                           | R1    | R1    | R1   |

| 010                           | R2    | R2    | R2   |

| 011                           | R3    | R3    | R3   |

| 100                           | R4    | R4    | R4   |

| 101                           | R5    | R5    | R5   |

| 110                           | R6    | R6    | R6   |

| 111                           | R7    | R7    | R7   |

| Encoding of ALU operations                                                                      |                                                                                                                      |                                                                                        |                                                                                |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| OPR                                                                                             | Operation                                                                                                            | Outcome                                                                                | Symbol                                                                         |

| 00000<br>00001<br>00010<br>00101<br>00110<br>01000<br>01010<br>01100<br>01110<br>10000<br>10001 | Transfer<br>Increment<br>Add<br>Subtract<br>Decrement<br>And<br>Or<br>Xor<br>Complement<br>Shift Right<br>Shift Left | A<br>A+1<br>A + B<br>A - B<br>A - 1<br>A $\land$ B<br>A $\lor$ B<br>X $\oplus$ B<br>A' | TSFA<br>INCA<br>ADD<br>SUB<br>DECA<br>AND<br>OR<br>XOR<br>COMA<br>SHRA<br>SHLA |

- Example of ALU Microoperation using the 3-address format

- Unary operation like Increment Register needs a source and destination (can be the same, too)

| ALU Microoperations: Example                                                                                                                                                                                                |                                                 |                                    |                                            |                                                          |                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------------|--------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Microoperation                                                                                                                                                                                                              | SELA                                            | SELB                               | SELD                                       | OPR                                                      | Control Word                                                                                   |

| $\begin{array}{l} R1 \leftarrow R2 - R3 \\ R4 \leftarrow R4 \land R5 \\ R6 \leftarrow R6 + 1 \\ R7 \leftarrow R1 \\ Output \leftarrow R2 \\ Output \leftarrow Input \\ R4 \leftarrow shl R4 \\ R5 \leftarrow 0 \end{array}$ | R2<br>R4<br>R6<br>R1<br>R2<br>Input<br>R4<br>R5 | R3<br>R5<br>-<br>-<br>-<br>-<br>R5 | R1<br>R6<br>R7<br>None<br>None<br>R4<br>R5 | SUB<br>OR<br>INCA<br>TSFA<br>TSFA<br>TSFA<br>SHLA<br>XOR | 010 011 001 00101<br>100 101 100 01010<br>110 000 110 00001<br>001 000 111 00000<br>010 000 00 |

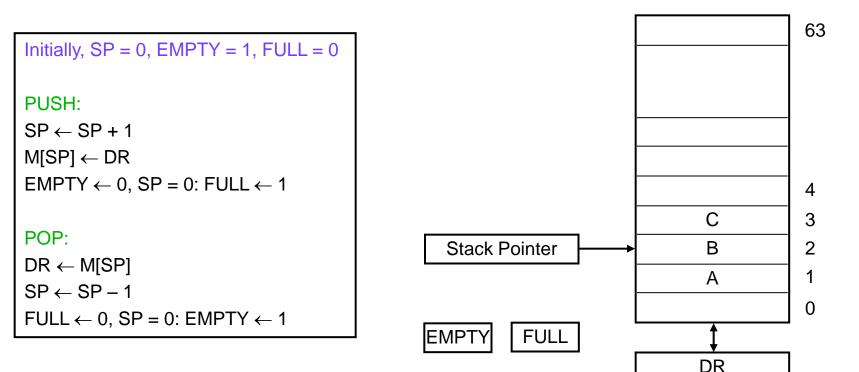

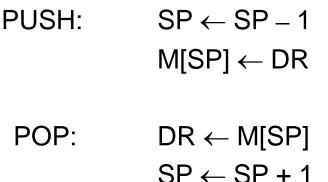

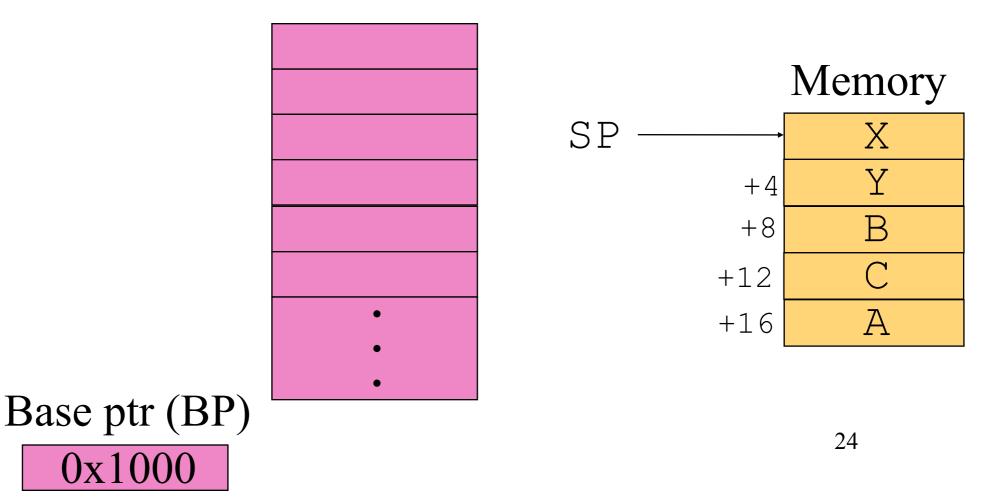

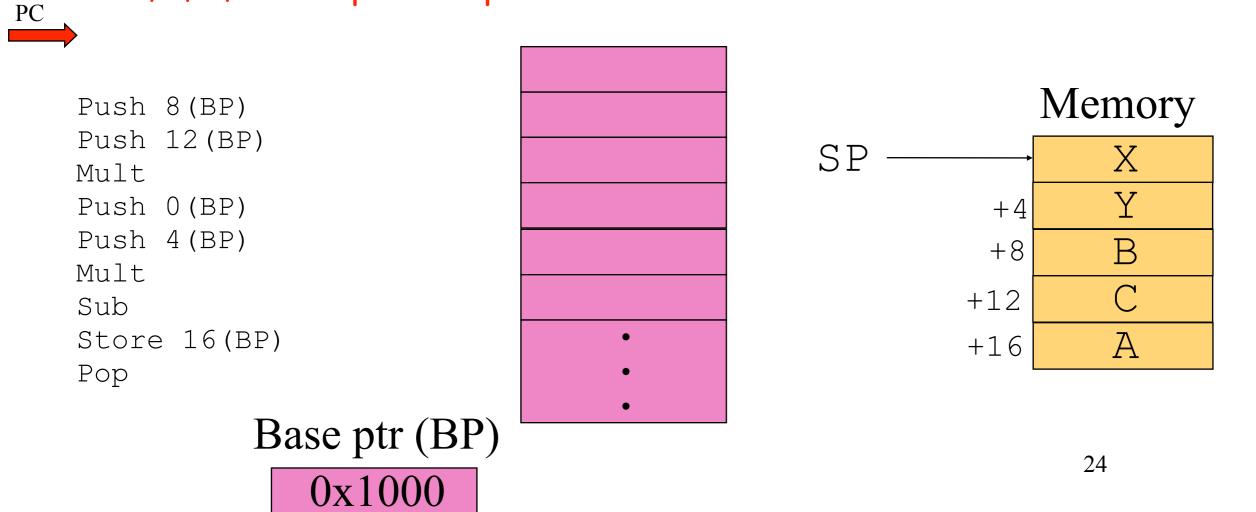

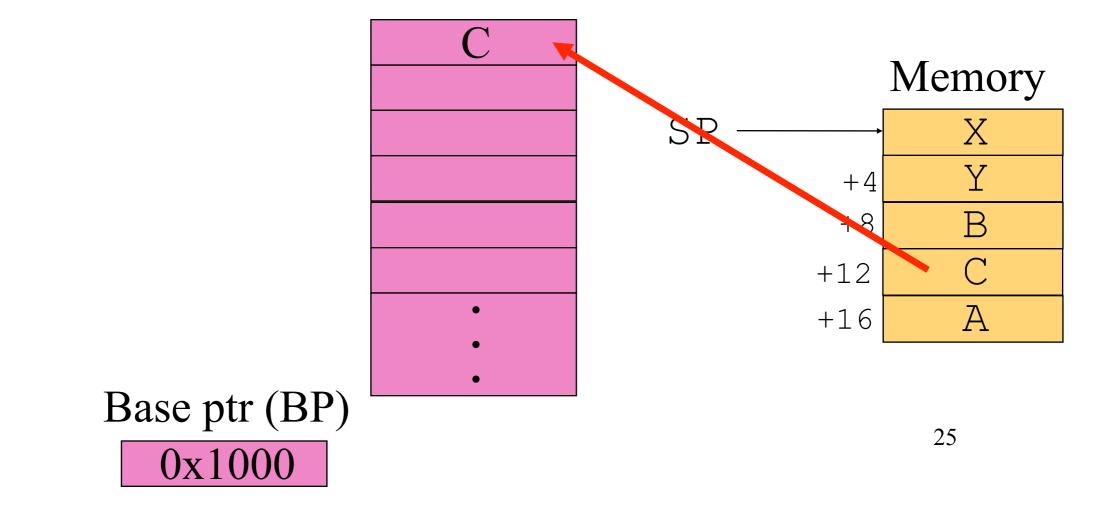

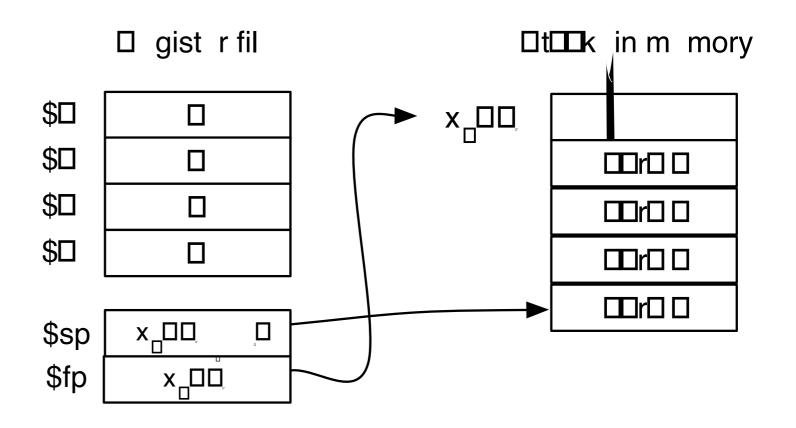

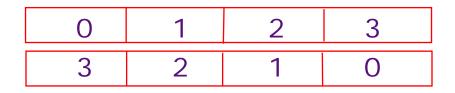

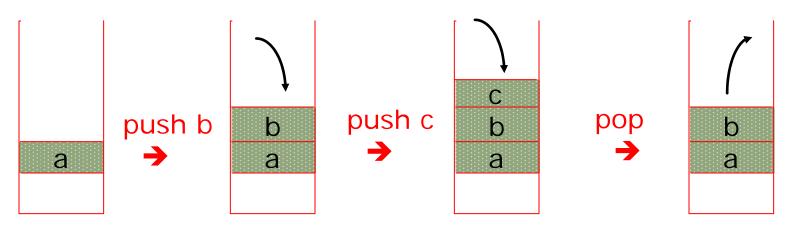

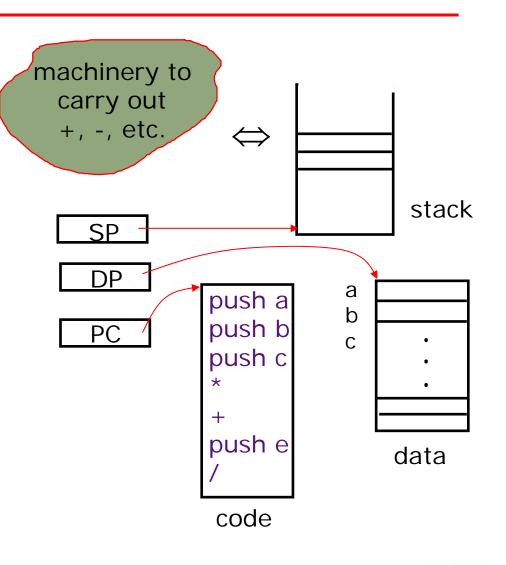

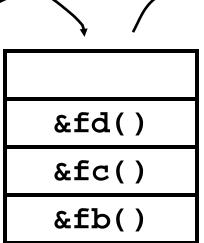

#### **Register Stack Organization**

- Useful in nested subroutines and nested loops control

- Efficient for arithmetic expression evaluation

- □ LIFO; only PUSH and POP operations are applicable

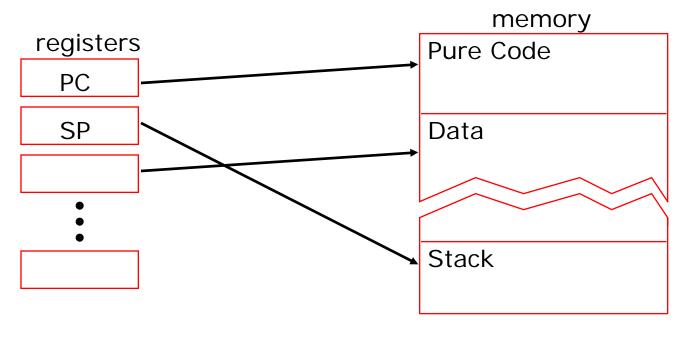

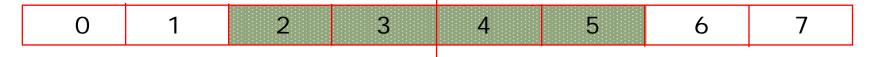

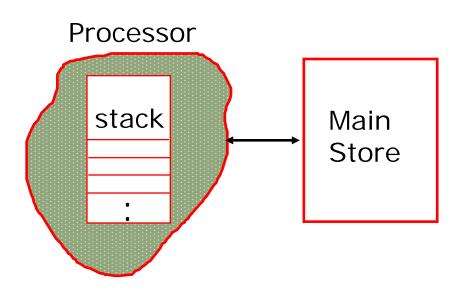

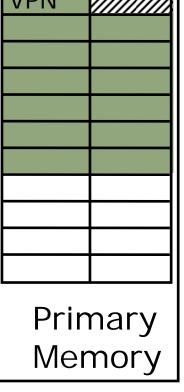

#### **Memory Stack Organization**

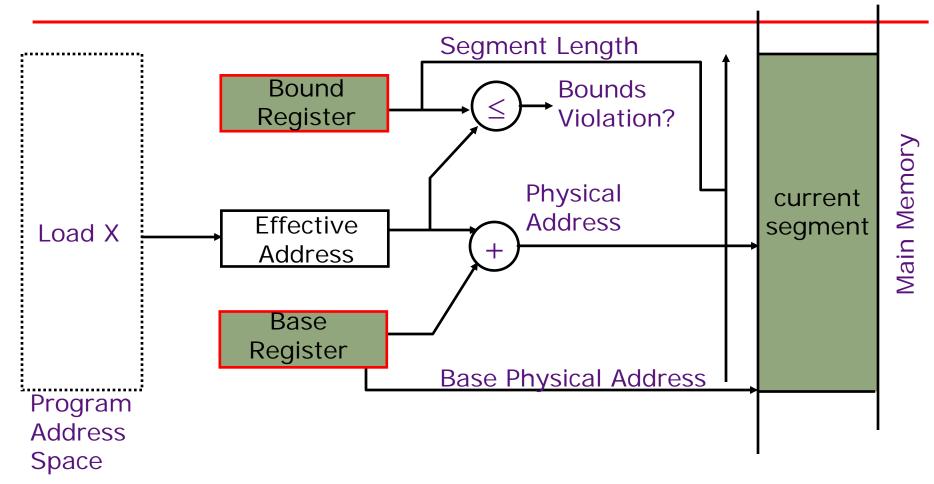

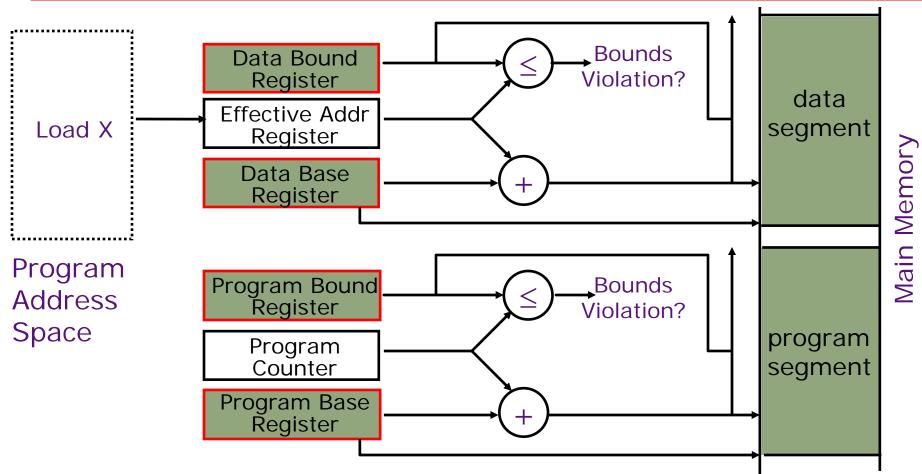

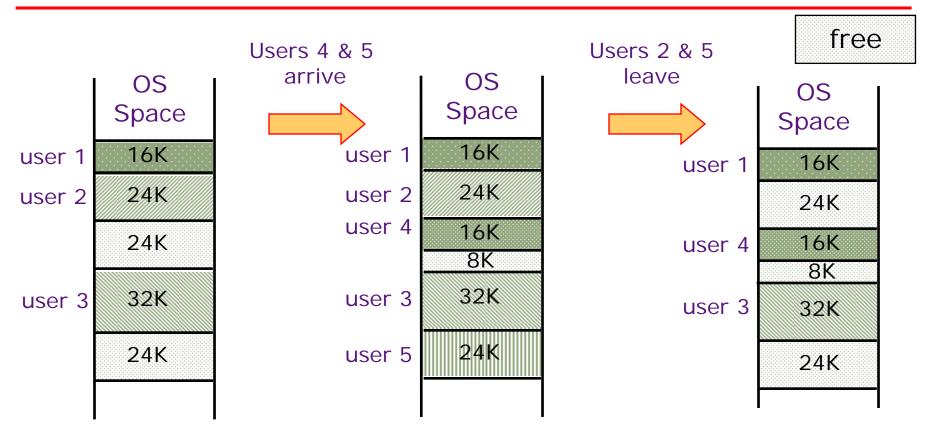

- Memory with Program, Data, and Stack Segments

- Portion of memory used as stack with a register as a stack pointer

- Check overflow & underflow

- Initially, SP is set to the end of memory (FFF)

- Stack overflows if it exceeds some limit

- Operations:

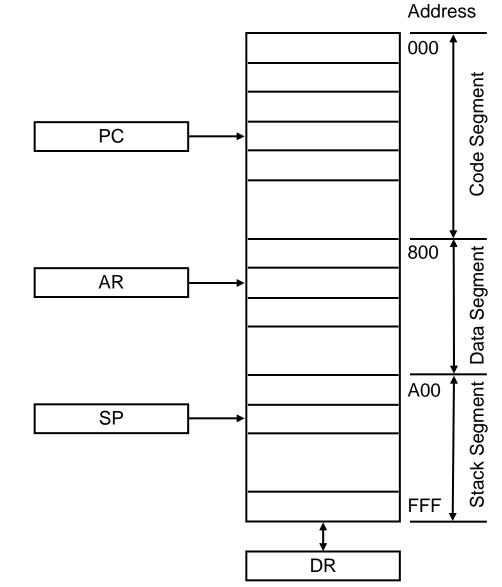

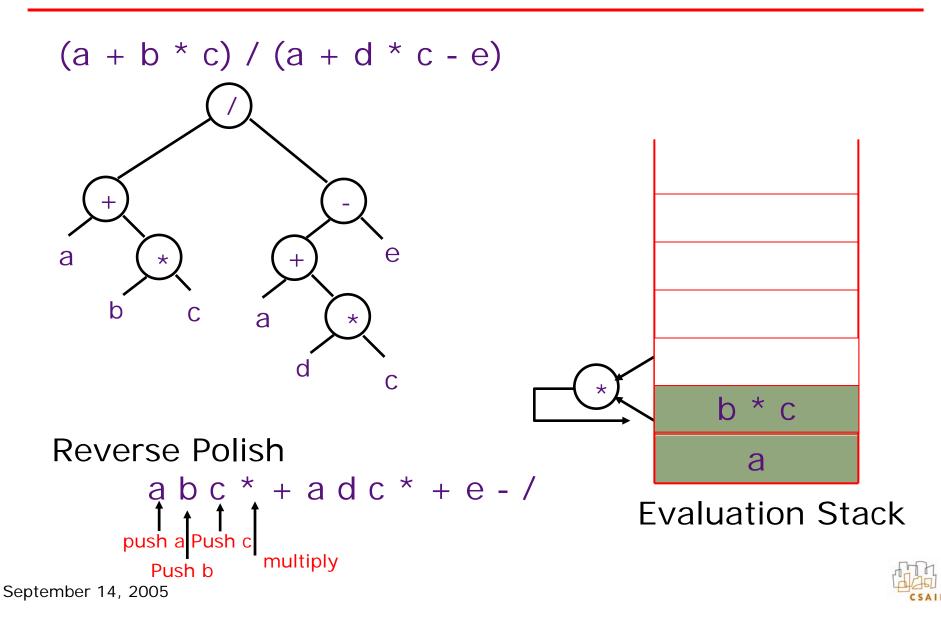

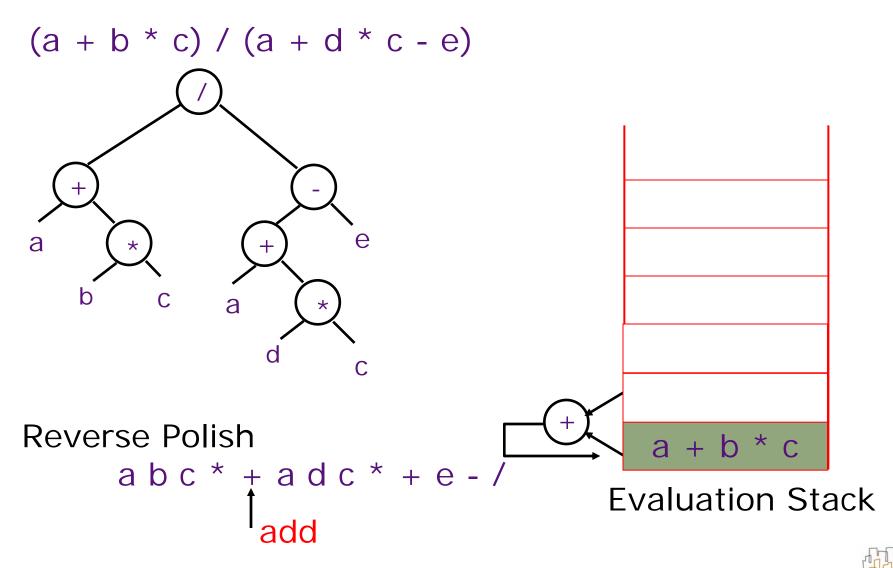

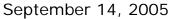

- Consider the arithmetic expressions: A + B

- + A B Prefix or Polish notation

- A B + Postfix or Reverse Polish notation

- Reverse Polish Notation is suitable for evaluation using stack

- Any arithmetic expression can be expressed in parenthesis-free

- Example: RPN of expression (3 \* 4) + (5 \* 6) is 3 4 \* 5 6 \* +

- Arrow stands for the top of the stack

Dr. T. Eldos

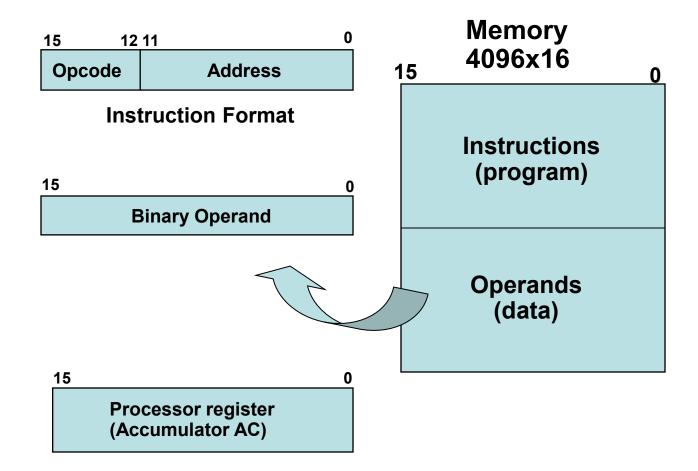

- Instruction Fields

- OP-code; specifies the operation to be performed

- Address; designates memory addresses or a processor registers

- Mode; specifies the way operand or effective address is determined

- Number of address fields in the instruction format depends on the internal organization. Most common organizations are:

- Single accumulator organization:

- \* ADD X ;  $AC \leftarrow AC + M[X]$

- Register organization:

| * | ADD | R1, R2, R3 | ; R1 ← R2 + R3   |

|---|-----|------------|------------------|

| * | ADD | R1, R2     | ; R1 ← R1 + R2   |

| * | ADD | R1, X      | ; R1 ← R1 + M[X] |

- Stack organization:

- $* \text{ PUSH } X \qquad \qquad ; \text{TOS} \leftarrow \text{M}[X]$

- \* ADD

#### 0-address & 1-address instructions

• 0-address, used in a stack computers; evaluate X = (A + B) \* (C + D):

| PUSH | А | ; TOS ← A                            |

|------|---|--------------------------------------|

| PUSH | В | ; TOS ← B                            |

| ADD  |   | ; TOS ← (A + B)                      |

| PUSH | С | ; TOS ← C                            |

| PUSH | D | ; TOS ← D                            |

| ADD  |   | ; TOS $\leftarrow$ (C + D)           |

| MUL  |   | ; TOS $\leftarrow$ (C + D) * (A + B) |

| POP  | Х | ; M[X] ← TOS                         |

□ 1-address, implies AC for manipulation; evaluate X = (A + B) \* (C + D):

| LOAD  | А | ; AC ← M[A]                 |

|-------|---|-----------------------------|

| ADD   | В | ; AC $\leftarrow$ AC + M[B] |

| STORE | Т | ; M[T] ← AC                 |

| LOAD  | С | ; AC ← M[C]                 |

| ADD   | D | ; AC $\leftarrow$ AC + M[D] |

| MUL   | Т | ; AC $\leftarrow$ AC * M[T] |

| STORE | Х | ; $M[X] \leftarrow AC$      |

#### 2-address & 3-address Instruction

• 2-address, evaluate X = (A + B) \* (C + D)

| MOV | R1, A  | ; R1 ← M[A]                 |

|-----|--------|-----------------------------|

| ADD | R1, B  | ; R1 ← R1 + M[B]            |

| MOV | R2, C  | ; R2 ← M[C]                 |

| ADD | R2, D  | ; R2 $\leftarrow$ R2 + M[D] |

| MUL | R1, R2 | ; R1 ← R1 * R2              |

| MOV | X, R1  | ; M[X] ← R1                 |

• 3-address, evaluate X = (A + B) \* (C + D)

| ADD | R1, A, B  | ; R1 $\leftarrow$ M[A] + M[B] |

|-----|-----------|-------------------------------|

| ADD | R2, C, D  | ; R2 $\leftarrow$ M[C] + M[D] |

| MUL | X, R1, R2 | ; M[X] ← R1 * R2              |

Compared to the 2-address instructions, 3-address results in short programs but instruction becomes long (many bits)

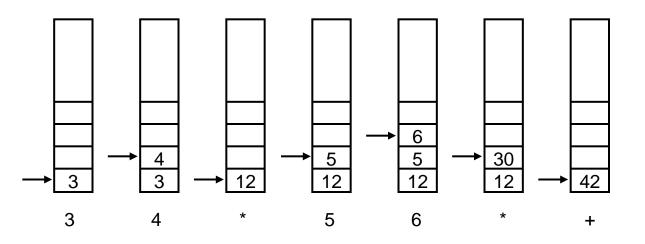

- Techniques, methods or ways by which the instruction accesses its operand

- Specifies a rule for interpreting or modifying the address field of the instruction (before the operand is actually referenced)

- Many addressing modes for flexibility and efficient use of bits

- Types are:

- Implied

- Immediate

- Absolute (Direct Address)

- Register Direct

- Register Indirect

- Register Indirect with Autoincrement and Autodecrement

- Relative:

- > PC relative

- Index relative

- Base relative

- Implied Mode

- Address of operand specified implicitly in the instruction

- No need to specify address in the instruction

- Example: effective address of CMA is AC and that of POP is stack pointer

- Immediate Mode

- Instead of specifying the address, operand itself is specified

- > No need to specify address, operand itself needs to be specified

- Sometimes, require more bits than the address

- Fast to acquire an operand

- > Example: LD #129, R1, source is immediate

- Register Mode

- Address specified in the instruction is the register address

- > Designated operand need to be in a register

- Shorter address than the memory address

- Saving address field in the instruction

- Faster to acquire an operand than the memory addressing

- > Example: MOV R1, R2, source and destinations are register direct

- Register Indirect Mode

- Instruction specifies a register containing address of operand

- Saving instruction bits since register address is shorter than memory address

- > Slower to acquire an operand than both register and memory addressing

- > Example: MOV R1, (R4), destination is memory whose address is in R4

- Register Indirect with Autoincrement/Autodecrement

- Register based addressing is automatically adjusted by incrementing or decrementing [some processor restrict the use to ()+ and –()]

- > Automatically adjust the pointers by adding proper offset

- > Example: ST R1, (R4)+

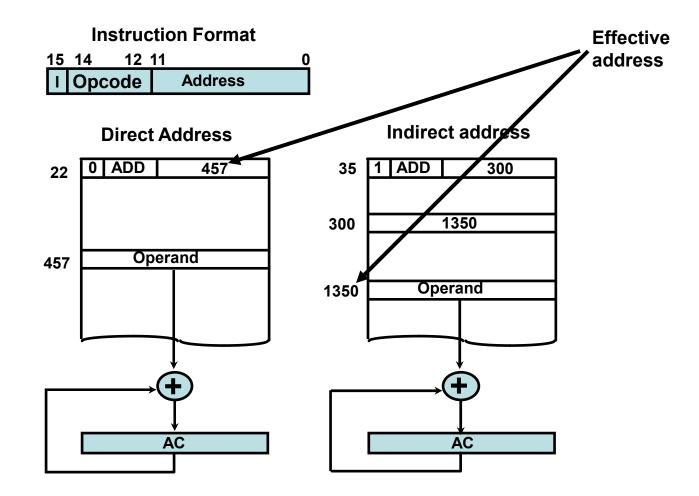

- Absolute or Direct Address Mode

- Instruction specifies directly the memory address of the operand

- Faster than the other memory addressing modes

- > Too many bits are needed to specify the address for a large memory space

- Example: ST #\$12, 124400, destination is operand at address 124400

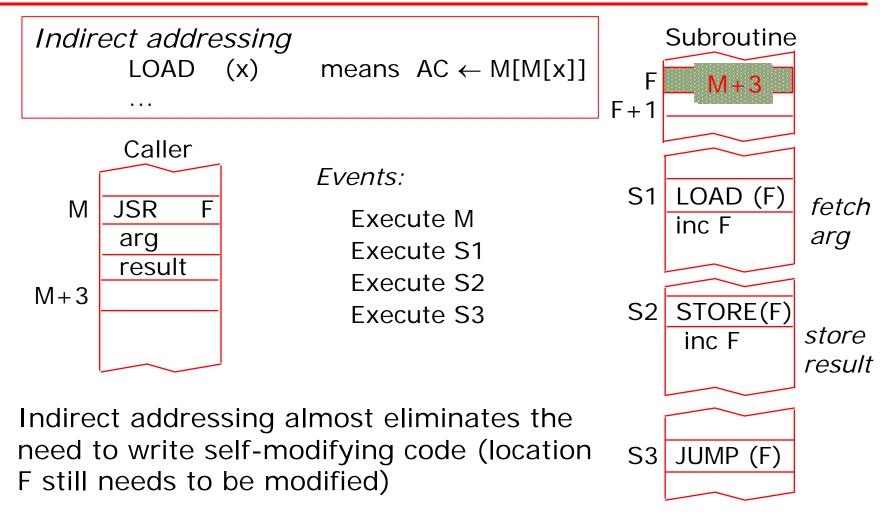

- Indirect Addressing Mode

- \* Address field specifies address to address of operand in memory

- Abbreviated address is used to address operand using small number of bits

- Slow to acquire an operand because of an additional memory access

- > Example: ST R1, (124400), destination address is at address 124400

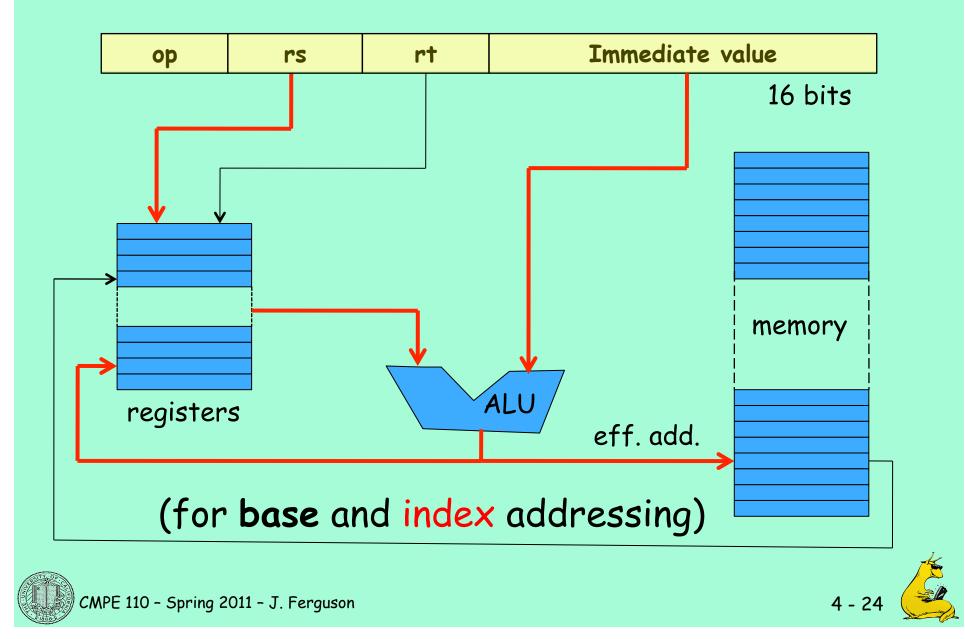

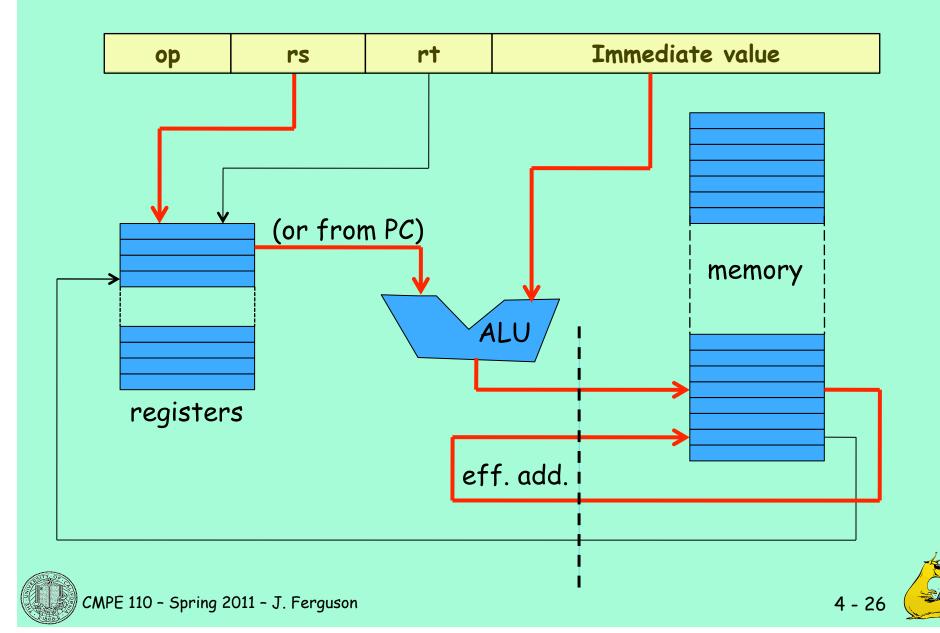

- Relative Addressing Modes

- Address fields of an instruction specifies part of the address which can be used along with a designated register to calculate operand address

- > Address field of the instruction is short

- Large physical memory can be accessed with a small number of address bits

- Example: Operand is at address formed modifying a special purpose register

- \* 3 different Relative Addressing Modes depending on register:

- > PC Relative, effective address is PC + offset, like BRA Loop

- Indexed

- Base Register

#### Addressing Modes: Example

- Highest frequency

- Transfer data between registers and memory or input-output devices

| Typical Data | a Transfer Instructions |

|--------------|-------------------------|

| Mnemonic     | Name                    |

| LD           | Load                    |

| ST           | Store                   |

| MOV          | Move                    |

| EX           | Exchange                |

| EXX          | Exchange All            |

| SWP          | Swap                    |

| IN           | Input                   |

| OUT          | Output                  |

| PUSH         | Push                    |

| POP          | Pop                     |

|                                                                                                                                                                    | ctions with Different Addressing Modes<br>Assembler ConventionRegister Transfer                  |                                                                                                                                                                                                                                                                                                                                             |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Direct address<br>Indirect address<br>Relative address<br>Immediate operand<br>Index addressing<br>Register<br>Register indirect<br>Autoincrement<br>Autodecrement | LD ADR<br>LD @ADR<br>LD \$ADR<br>LD #NBR<br>LD ADR(X)<br>LD R1<br>LD (R1)<br>LD (R1)+<br>LD (R1) | $\begin{array}{l} AC \leftarrow M[ADR] \\ AC \leftarrow M[M[ADR]] \\ AC \leftarrow M[PC + ADR] \\ AC \leftarrow M[PC + ADR] \\ AC \leftarrow NBR \\ AC \leftarrow MBR \\ AC \leftarrow M[R1] \\ AC \leftarrow R1 \\ AC \leftarrow R1 \\ AC \leftarrow M[R1], R1 \leftarrow R1 + 1 \\ R1 \leftarrow R1 - 1, AC \leftarrow M[R1] \end{array}$ |  |

#### Instruction Types: Arithmetic Operations

Some processors include FP and/or BCD arithmetic

| Arithmetic Instructions<br>Mnemonic Name |                         |  |

|------------------------------------------|-------------------------|--|

| INC                                      | Increment               |  |

| DEC                                      | Decrement               |  |

| ADD                                      | Add                     |  |

| SUB                                      | Subtract                |  |

| MUL                                      | Multiply                |  |

| DIV                                      | Divide                  |  |

| ADDC                                     | Add with Carry          |  |

| SUBB                                     | Subtract with Borrow    |  |

| NEG                                      | Negate (2's Complement) |  |

| Logical and Bit M<br>Mnemonic                                      | Name Mnemonic                                                                                                                                  |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| CLR<br>COM<br>AND<br>OR<br>XOR<br>CLRC<br>SETC<br>COMC<br>EI<br>DI | Clear<br>Complement<br>AND<br>OR<br>Exclusive-OR<br>Clear carry CLRC<br>Set Carry<br>Complement Carry<br>Enable Interrupt<br>Disable Interrupt |

| Shift Instructions<br>Mnemonic | Name Mnemonic           |

|--------------------------------|-------------------------|

| SHR                            | Logical Shift Right     |

| SHL                            | Logical Shift Left      |

| SHRA                           | Shift Right Arithmetic  |

| SHLA                           | Shift Left Arithmetic   |

| ROR                            | Rotate Right            |

| ROL                            | Rotate Left             |

| RORC                           | Rotate Right thru Carry |

| ROLC                           | Rotate Left thru Carry  |

#### **Instruction Types: Program Control**

- PC is updated in two major ways;

- By incrementing

- Fetch from the fall through path

- > Skip the next instruction to the next

- By loading

- Jump to an address

- Branch to an address

- Call subroutine

- Return to the calling part of the program

| Program Control | Instructions        |

|-----------------|---------------------|

| Mnemonic        | Name                |

| BR              | Branch              |

| JMP             | Jump                |

| SKP             | Skip                |

| CALL            | Call Subroutine     |

| RTN             | Return              |

| CMP             | Compare (using SUB) |

| TST             | Test (using AND)    |

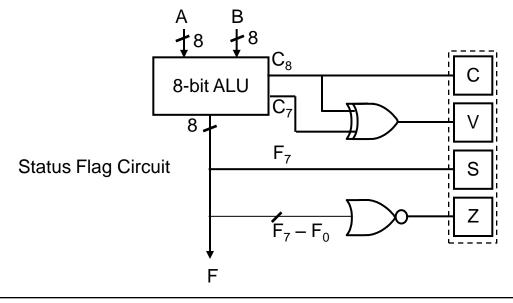

#### **Condition Codes**

- The recent state of the machine is expressed in flip-flops collectively called:

- Flags

- Status register

- Condition Code Register

- The S (sometimes called N) for Sign or Negative, it reflects the sign of the outcome, that is why it is a copy of the MSB of the ALU

- The Z (Zero) flag is set when all the bits of the result are 0's

- The C (Carry) and V (oVerflow) flags are meant to reflect the carry for the unsigned and signed

| Simple Compare Condition<br>Branch Condition | Tested condition | Mnemonic |

|----------------------------------------------|------------------|----------|

| Branch if Zero                               | Z = 1            | BZ       |

| Branch if Not Zero                           | Z = 0            | BNZ      |

| Branch if Carry                              | C = 1            | BC       |

| Branch if No Carry                           | C = 0            | BNC      |

| Branch if Plus                               | S = 0            | BP       |

| Branch if Minus                              | S = 1            | BM       |

| Branch if oVerflow                           | V = 1            | BV       |

| Branch if No oVerflow                        | V = 0            | BNV      |

#### **Arithmetic Compare Conditions**

| Unsigned Compare condition        | ons (A - B) |               |            |  |

|-----------------------------------|-------------|---------------|------------|--|

| Branch Condition                  | Tested      | Condition     | Mnemonic   |  |

| Dranah if Highar                  | A > B       | C' . Z'       | DLI        |  |

| Branch if Higher                  |             | -             | BHI        |  |

| Branch if Higher or Equal         | $A \ge B$   | C'            | BHE or BNC |  |

| Branch if Lower                   | A < B       | C             | BLO or BC  |  |

| Branch if Lower or Equal          | $A \leq B$  | C + Z         | BLOE       |  |

|                                   |             |               |            |  |

| Signed Compare Conditions (A - B) |             |               |            |  |

| Branch Condition                  | Tested      | Condition     | Mnemonic   |  |

| Branch if Greater Than            | A > B       | (N ⊕ V)' . Z' | BGT        |  |

| Branch if Greater or Equal | $A \ge B$  | (N ⊕ V)'           | BGE |

|----------------------------|------------|--------------------|-----|

| Branch if Less Than        | A < B      | $(N \oplus V)$     | BLT |

| Branch if Less or Equal    | $A \leq B$ | $(N \oplus V) + Z$ | BLE |

| Signed & Unsigned Compare conditions (A - B) |        |           |            |  |

|----------------------------------------------|--------|-----------|------------|--|

| Branch Condition                             | Tested | Condition | Mnemonic   |  |

|                                              |        |           |            |  |

| Branch if Equal                              | A = B  | Z         | BEQ or BZ  |  |

| Branch if Not Equal                          | A ≠ B  | Z'        | BNE or BNZ |  |

|                                              |        |           |            |  |

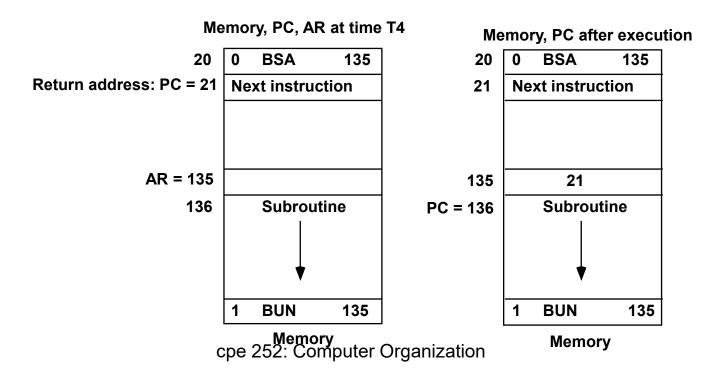

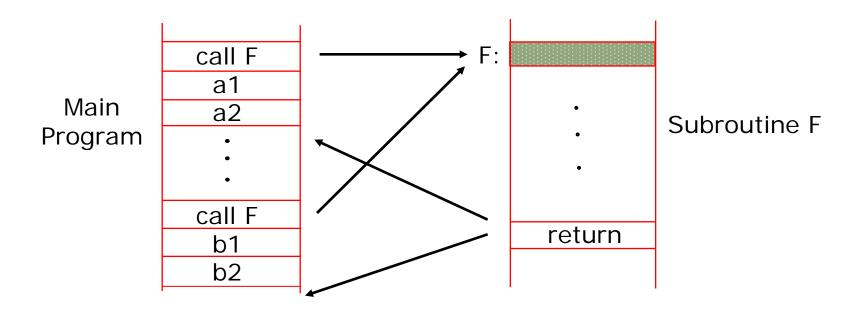

#### Subroutine Call & Return

- Subroutine calls have flavors: Call, Jump and Branch

- Two Most Important Operations are Implied:

- \* Save Return Address (current value of PC) for proper operation

- Locations for storing Return Address

- > Fixed Location in the subroutine area

- Fixed Location in memory

- Special register within the processor

- > Memory stack, which is the most efficient way

- Branch to the beginning of the subroutine by placing effective address into the PC

- Stack Based Microoperations:

- $* \mathsf{RTN} \qquad \mathsf{PC} \leftarrow \mathsf{M[SP]}$

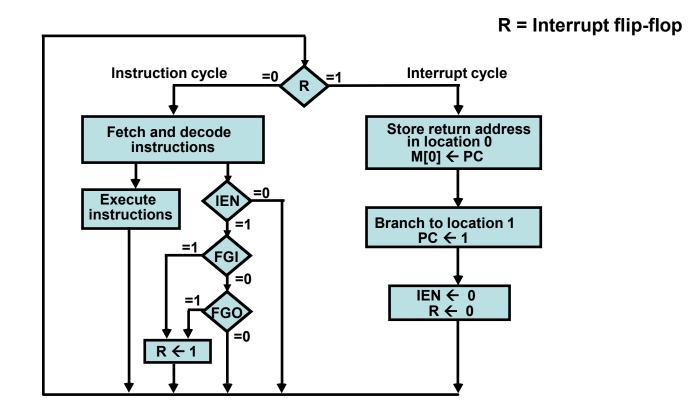

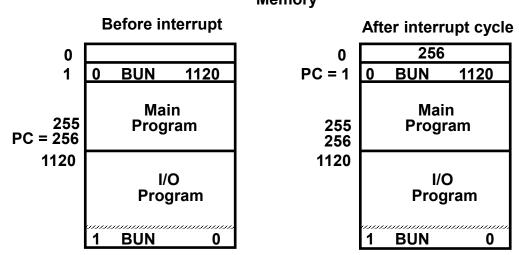

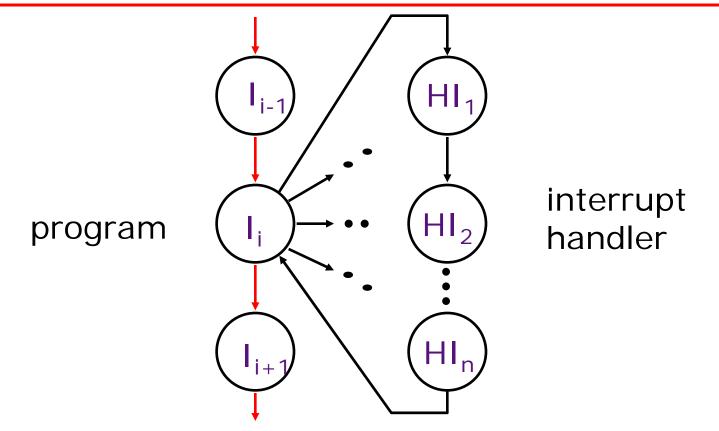

#### Program Interrupt - Types

- External interrupts; initiated from external devices

- Input-Output Device; data transfer start & stop

- Timing Device

- Power Failure

- Operator; a pushbutton

- Internal interrupts (traps); caused by a running program

- Register Check

- Stack Overflow

- Divide by zero

- OP-code Violation (illegal instruction)

- Protection Violation

- Software Interrupts; initiated by executing an instruction

- Supervisor Call; to switch from the user mode to the supervisor mode

- Interrupts are two types:

- \* Hardware, or external interrupt, usually initiated by an external event

- Software, or internal interrupt, due to instruction execution

- The address of the interrupt service program is determined by:

- Hardware, requesting device send a vector

- Software, fixed address for each type

- An interrupt procedure usually stores all the information necessary to define the state of processor rather than storing only the PC

- The state of the processor is determined from;

- Content of the PC

- Content of all processor registers

- Content of status bits

- \* Saving the state of processor depends on the architecture

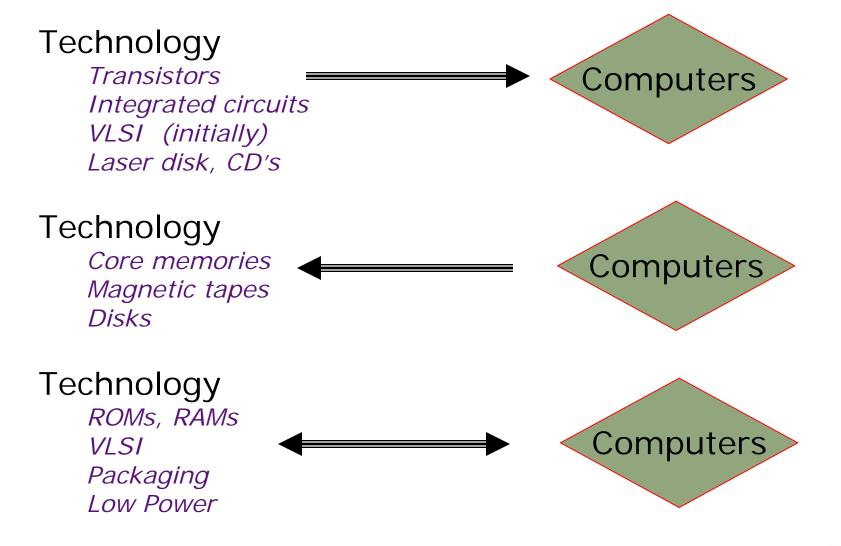

#### **Computer Architecture Trends**

- The instruction set is an important aspect of computer design

- The instruction set determines how the machine language programs are constructed

- Early 80's, stuck by marginal improvement in performance through technology, directed the effort towards the organization instead

- Ideas for improving the organization included:

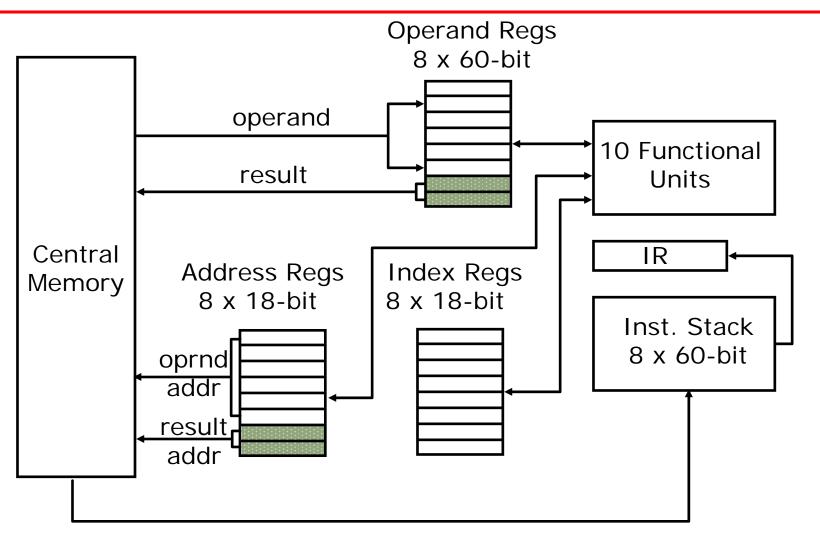

- Adding Registers, to localize the variables for high speed access

- Adding Caches, to keep data and instructions handy

- Adding Functional units, to overlap executions

- This would have increased the performance, but not with the limited integration level of 10<sup>5</sup> transistors/chip of that time

- Conventionally, control units used to eat up good deal of that, nearly 50%, but could reach 70% in some implementations

- The idea was to make the control unit less complex, taking only a fraction of that; say 5%

- Trends were then called:

- Reduced Instruction Set Computers (RISC) &

- Complex Instruction Set Computers (CISC)

- Both have good reasons to stay

- Differences are becoming less and less, as the number of transistors per package is no longer an issue;

- Registers are in abundance in both

- Cache is now in abundance in both and implemented in many levels

- Functional units are also many in both

- To stay backwardly compatible, a new trend is now in existence;

RISC core with CISC shell, P4 is just like that

#### **RISC & CISC**

- Instruction set size < 100</li>

- Addressing modes < 4</p>

- Control unit logic < 10%

- Memory access is restricted to Load/Store instructions

- Fixed length instructions

- Single cycle execution

- Most of the instructions are used

- Hardwired control unit

- Highly complier dependent for efficient code

- Because of less complex control unit, it has:

- Large number of registers > 128

- Larger caches

- More functional units

- Instructions set size, > 200

- Addressing modes > 8

- Control unit logic > 50%

- Memory access is allowed for data manipulation instructions

- variable length instructions

- Multiple cycle execution

- Some instructions are rarely used

- Microprogrammed control unit

- Compiler dependence is not as much

- Because of more complex control unit, it has:

- Small number of registers < 32</li>

- Smaller caches

- \* Less functional units

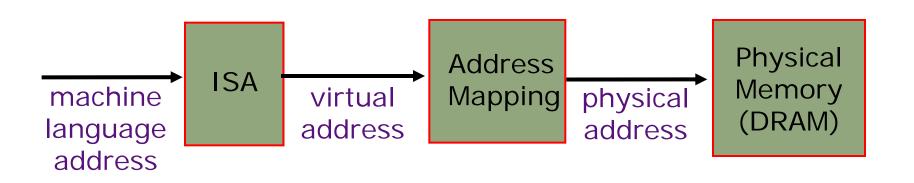

## Instruction Set Architectures: Talking to the Machine

# The Architecture Question

- How do we build computer from contemporary silicon device technology that executes general-purpose programs quickly, efficiently, and at reasonable cost?

- i.e. How do we build the computer on your desk.

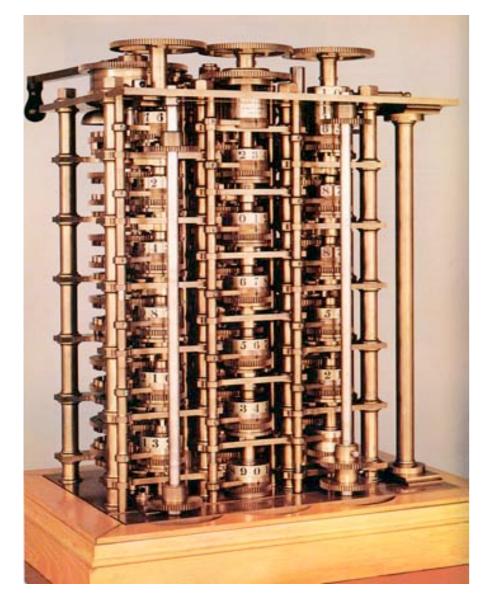

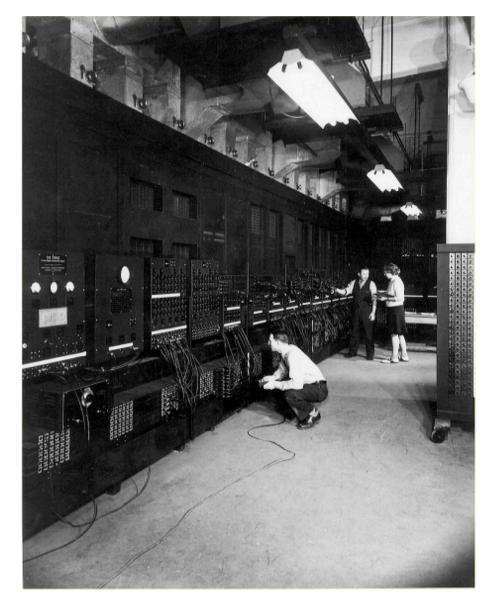

# In the beginning...

#### The Difference Engine

ENIAC

Physical configuration specifies the computation

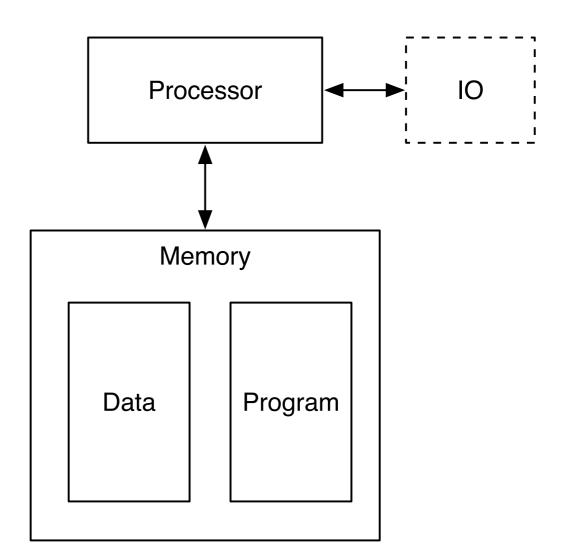

## The Stored Program Computer

- The program is data

- i.e., it is a sequence of *numbers* that machine interprets

- A very elegant idea

- The same technologies can store and manipulate programs and data

- Programs can manipulate programs.

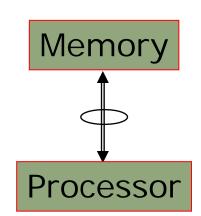

## The Stored Program Computer

- A very simple model

- Several questions

- How are program represented?

- How do we get algorithms out of our brains and into that representation?

- How does the the computer interpret a program?

# Representing Programs

- We need some basic building blocks -- call them "instructions"

- What does "execute a program" mean?

- What instructions do we need?

- What should instructions look like?

- Is it enough to just specify the instructions?

- How complex should an instruction be?

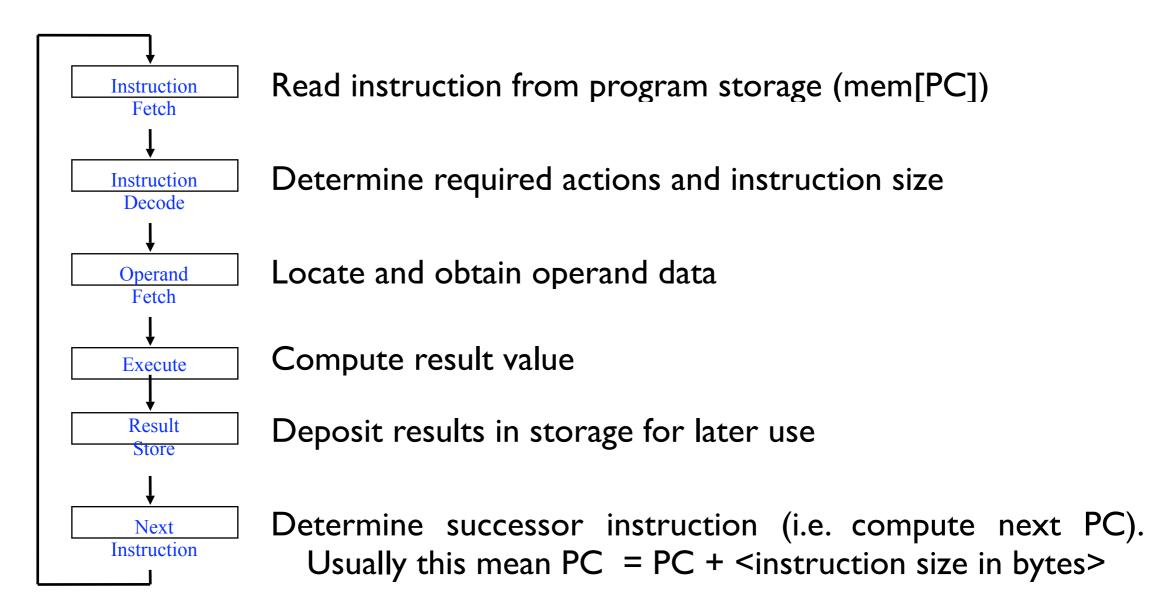

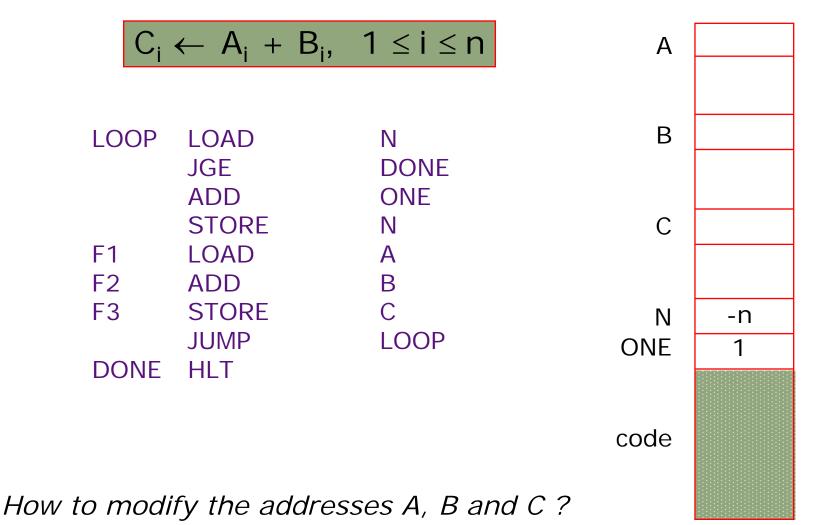

# Program Execution

- This is the algorithm for a stored-program computer

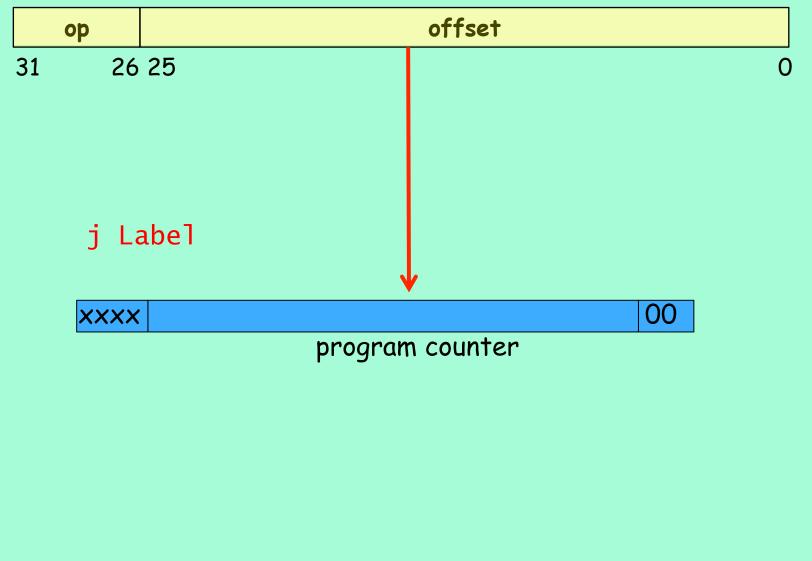

- The Program Counter (PC) is the key

# Motivating Code segments

- a = b + c;

- a = b + c + d;

- a = b & c;

- a = b + 4;

- a = b (c \* (d/2) 4);

- if (a) b = c;

- if (a == 4) b = c;

- while (a != 0) a--;

- $a = 0 \times DEADBEEF;$

- a = foo[4];

- foo[4] = a;

- a = foo.bar;

- a = a + b + c + d +... +z;

- a = foo(b); -- next class

# What instructions do we need?

- Basic operations are a good choice.

- Motivated by the programs people write.

- Math: Add, subtract, multiply, bit-wise operations

- Control: branches, jumps, and function calls.

- Data access: Load and store.

- The exact set of operations depends on many, many things

- Application domain, hardware trade-offs, performance, power, complexity requirements.

- You will see these trade-offs first hand in the ISA project and in 141L.

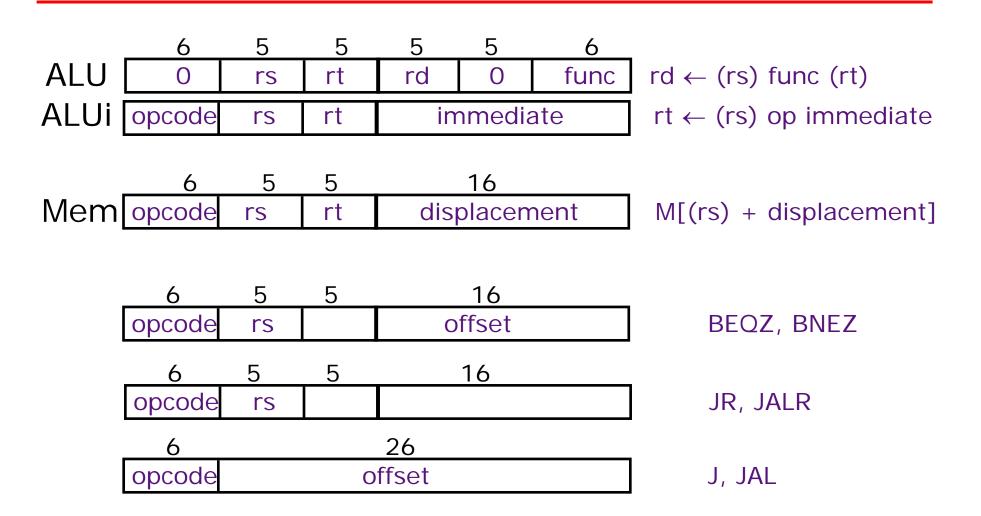

## What should instructions look like?

- They will be numbers -- i.e., strings of bits

- It is easiest if they are all the same size, say 32 bits

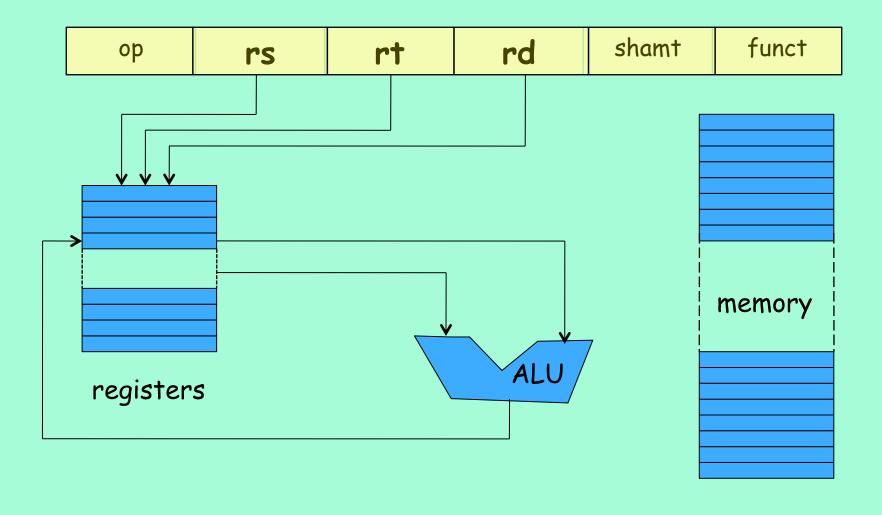

- We can break up these bits into "fields" -- like members in a class or struct.

- This sets some limits

- On the number of different instructions we can have

- On the range of values any field of the instruction can specify

## Is specifying the instructions sufficient?

- No! We also must what the instructions operate on.

- This is called the "Architectural State" of the machine.

- Registers -- a few named data values that instructions can operate on

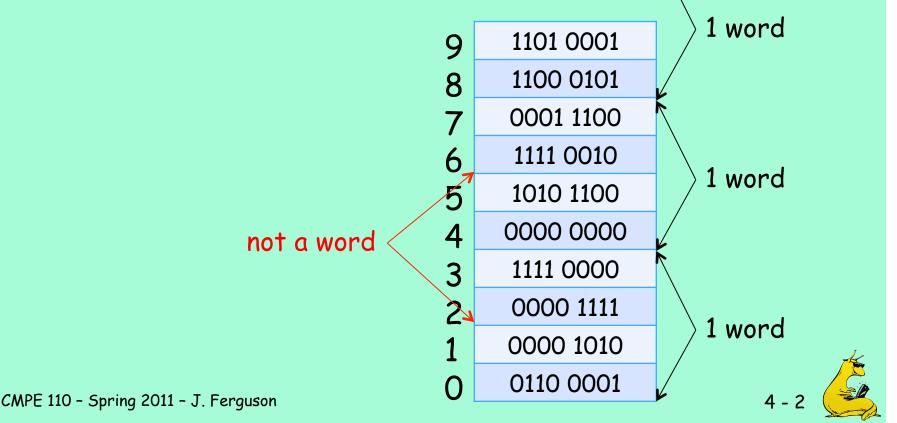

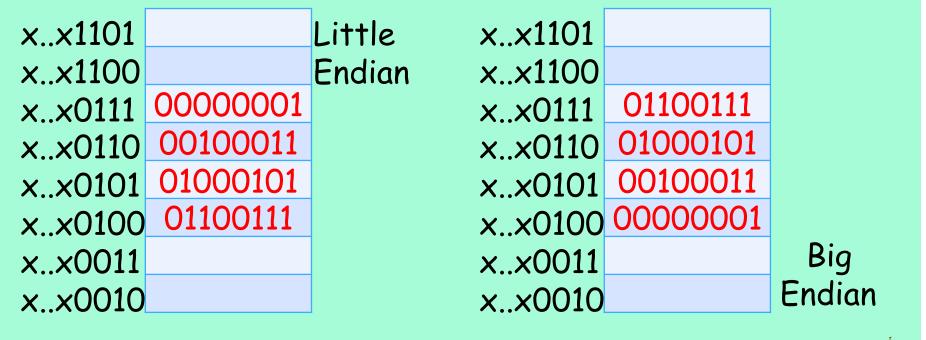

- Memory -- a much larger array of bytes that is available for storing values.

- How big is memory? 32 bits or 64 bits of addressing.

- 64 is the standard today for desktops and larger.

- 32 for phones and PDAs

- Possibly fewer for embedded processors

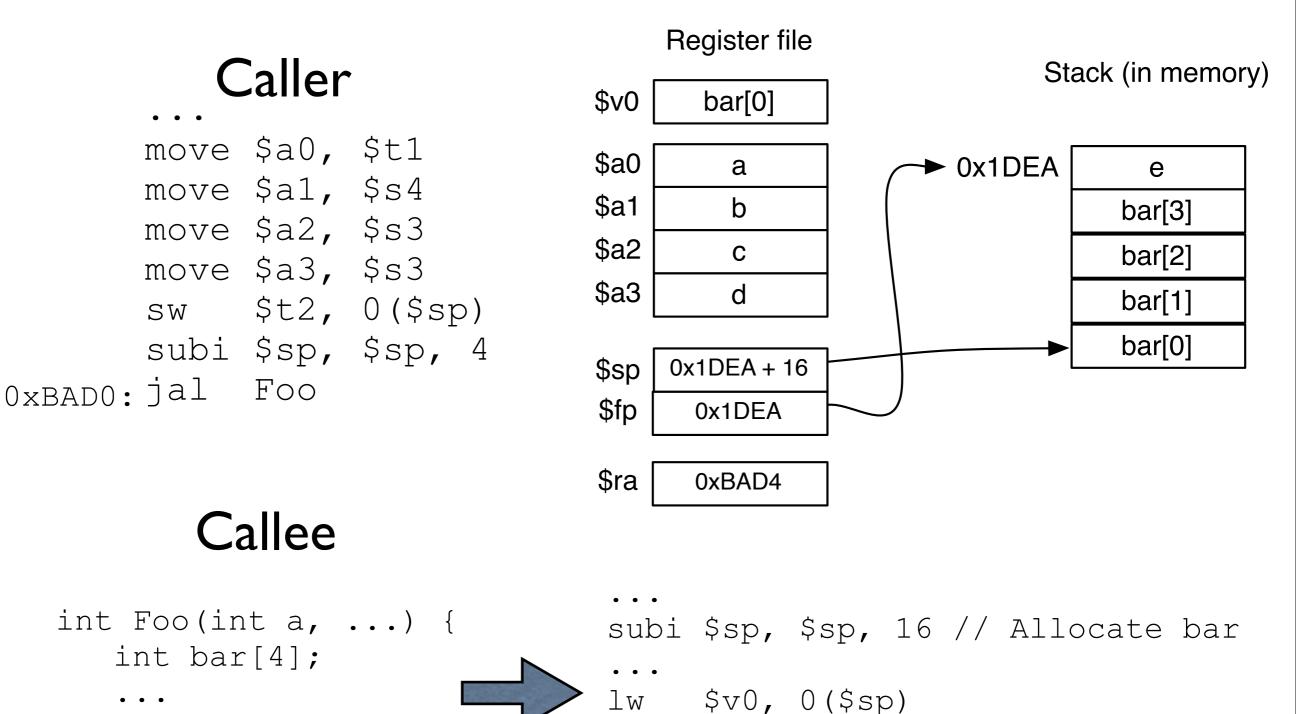

- We also need to specify semantics of function calls

- The "Stack Discipline," "Calling convention," or "Application binary interface (ABI)".

### How complex should instructions be?

#### • More complexity

- More different instruction types are required.

- Increased design and verification costs

- More complex hardware.

- More difficult to use -- What's the right instruction in this context?

- Less complexity

- Programs will require more instructions -- poor code density

- Programs can be more difficult for humans to understand

- In the limit, decremement-and-branch-if-negative is sufficient

- Imagine trying to decipher programs written using just one instruction.

- It takes many, many of these instructions to emulate simple operations.

- Today, what matters most is the compiler

- The Machine must be able to understand program

- A program must be able to decide which instructions to use

# Big "A" Architecture

- The Architecture is a contract between the hardware and the software.

- The hardware defines a set of operations, their semantics, and rules for their use.

- The software agrees to follow these rules.

- The hardware can implement those rules IN ANY WAY IT CHOOSES!

- Directly in hardware

- Via a software layer

- Via a trained monkey with a pen and paper.

- This is a classic interface -- they are everywhere in computer science.

- "Interface," "Separation of concerns," "API," "Standard,"

- For your project you are designing an Architecture -- not a processor.

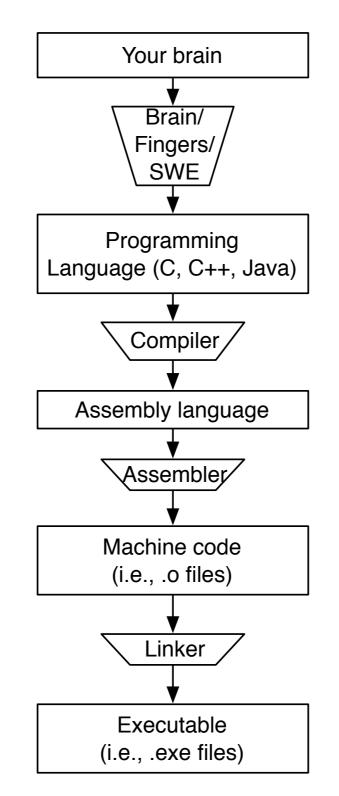

## From Brain to Bits

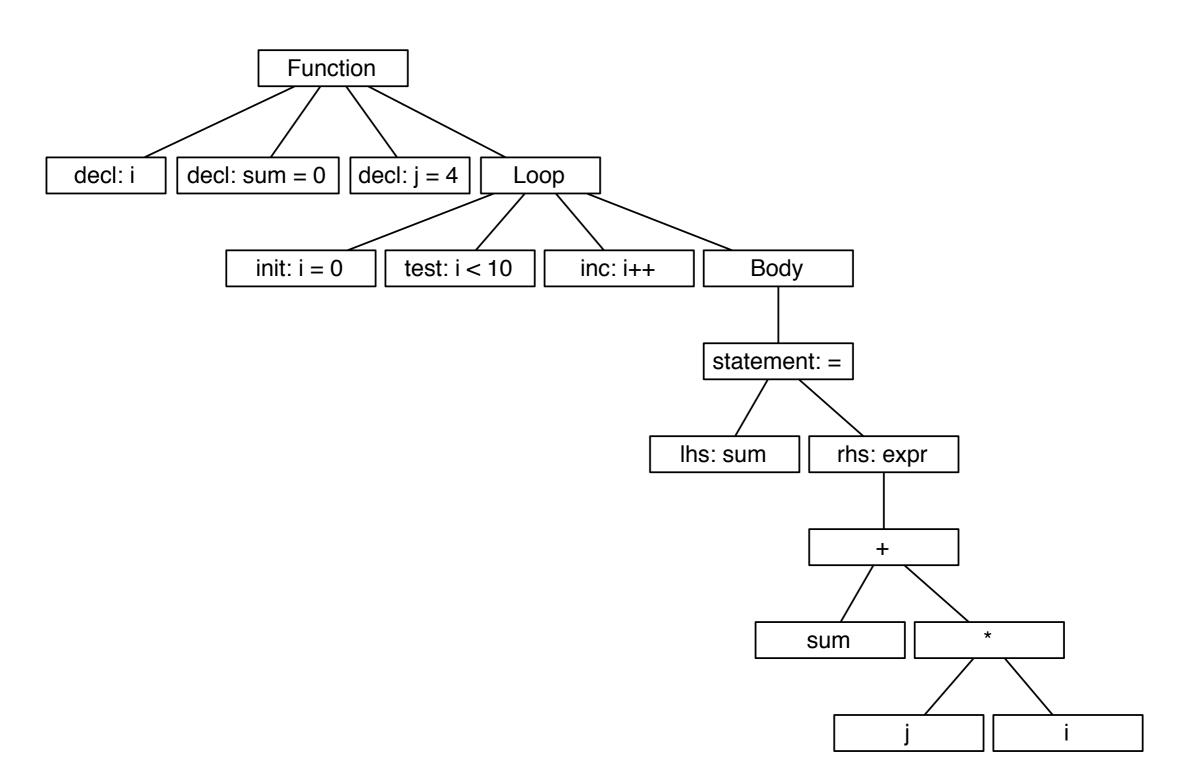

### C Code

```

int i;

int sum = 0;

int j = 4;

for(i = 0; i < 10; i++) {

sum = i * j + sum;

}

```

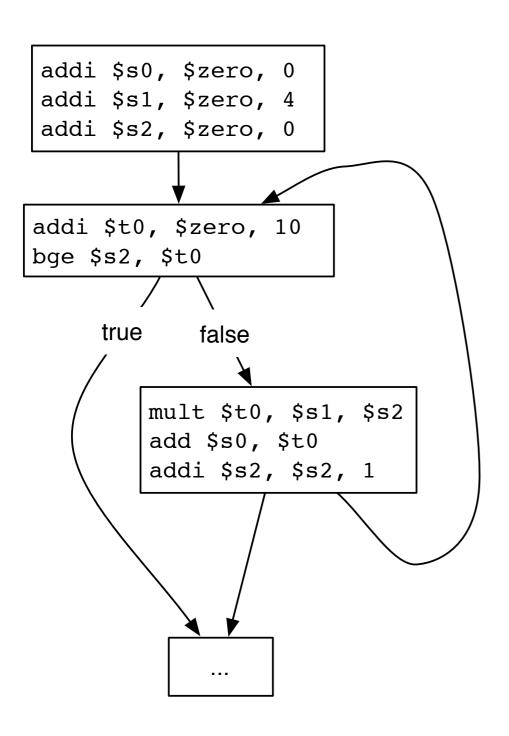

# In the Compiler

## In the Compiler

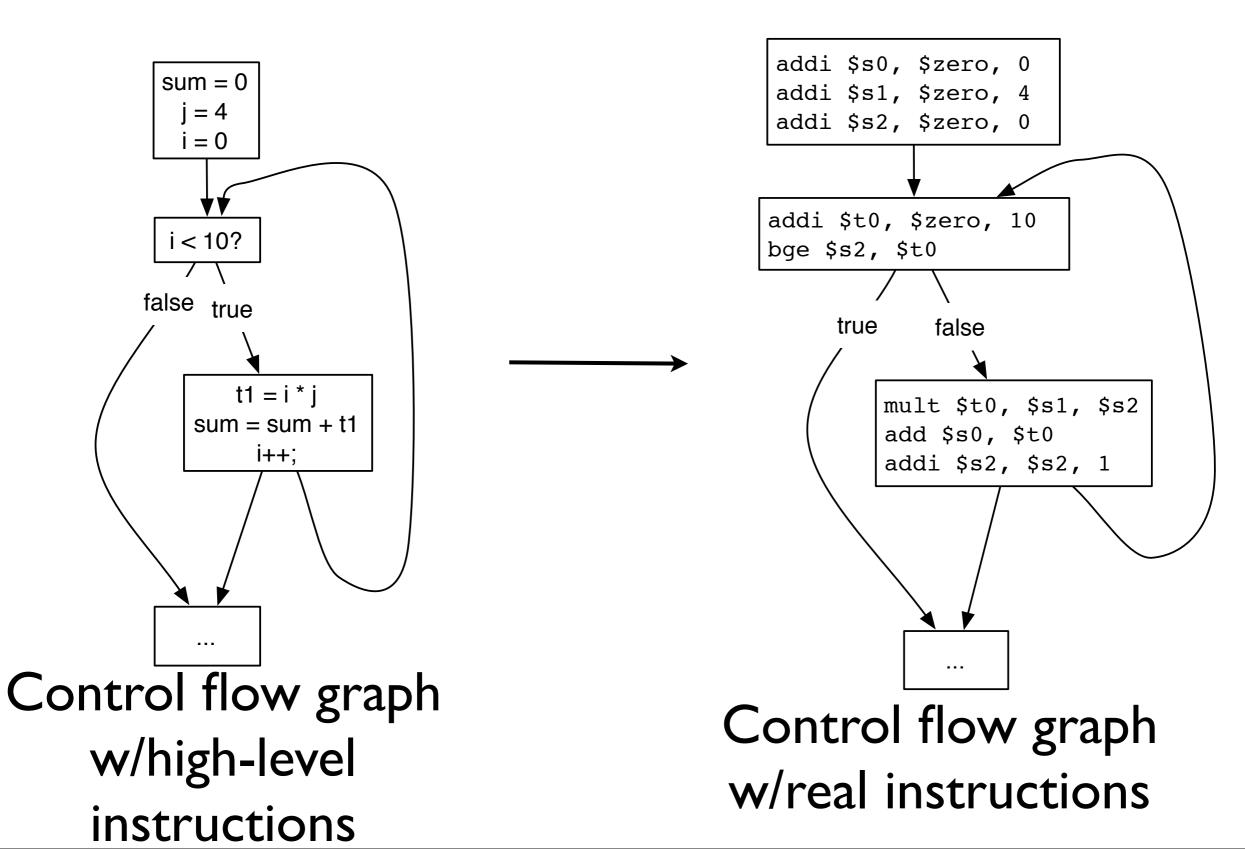

# Out of the Compiler

| addi | \$s0, | \$zero, | 0 |

|------|-------|---------|---|

| addi | \$s1, | \$zero, | 4 |

| addi | \$s2, | \$zero, | 0 |

top: addi \$t0, \$zero, 10 bge \$s2, \$t0, after

body: mult \$t0, \$s1, \$s2 add \$s0, \$t0 addi \$s2, \$s2, 1 br top

after:

• • •

Assembly language

## Labels in the Assembler

addi \$s0, \$zero, 0

addi \$s1, \$zero, 4

addi \$s2, \$zero, 0

top: addi \$t0, \$zero, 10 bge \$s2, \$t0, after 'after' is defined at 0x20used at 0x10The value of the immediate for the branch is 0x20-0x10 = 0x10

mult \$t0, \$s1, \$s2

add \$s0, \$t0

addi \$s2, \$s2, 1

br top

after:

'top' is defined at 0x0C used at 0x1C The value of the immediate for the branch is 0x0C-0x1C = 0xFFFF0 (i.e., -0x10)

• • •

## Labels in the Assembler

0x00 addi \$s0, \$zero, 0

0x04 addi \$s1, \$zero, 4

0x08 addi \$s2, \$zero, 0

top: 0x0C addi \$t0, \$zero, 10 0x10 bge \$s2, \$t0, after

mult \$t0, \$s1, \$s2

'after' is defined at 0x20used at 0x10The value of the immediate for the branch is 0x20-0x10 = 0x10

'top' is defined at 0x0C used at 0x1C The value of the immediate for the branch is 0x0C-0x1C = 0xFFFF0 (i.e., -0x10)

```

0x20 after:

```

br

0x1C

•••

0x14 add \$s0, \$t0

0x18 addi \$s2, \$s2, 1

top

# Assembly Language

#### • "Text section"

- Hold assembly language instructions

- In practice, there can be many of these.

- "Data section"

- Contain definitions for static data.

- It can contain labels as well.

- The addresses in the data section have no relation to the addresses in the data section.

- Pseudo instructions

- Convenient shorthand for longer instruction sequences.

```

void foo() {

static int a = 0;

a++;

...

```

```

.data

foo_a:

.word 0

```

```

.text

foo:

lda $t0, foo_a

ld $s0, 0($t0)

addi $s0, $s0, 1

st $s0, 0($t0)

after:

```

• • •

```

void foo() {

static int a = 0;

a++;

}

```

```

.data

foo_a:

.word 0

```

```

.text

foo:

lda $t0, foo_a

ld $s0, 0($t0)

addi $s0, $s0, 1

st $s0, 0($t0)

after:

```

• • •

lda \$t0, foo\_a

becomes these instructions (this is not assembly language!)

andi \$t0, \$zero, ((foo\_a & 0xff00) >> 16)

sll \$t0, \$t0, 16

andi \$t0, \$t0, (foo a & 0xff)

.data

```

foo a:

.word 0

void foo() {

static int a = 0;

.text

foo:

a++;

lda $t0, foo a

ld $s0, 0($t0)

addi $s0, $s0, 1

st $s0, 0($t0)

after:

lda $t0, foo a

becomes these instructions (this is not assembly language!)

andi $t0, $zero ((foo_a & 0xff00) >> 16)

sll $t0, $t0, 16

andi $t0, $t0, (foo a & 0xff)

```

#### The assembler computes and inserts these values.

```

.data

foo a:

.word 0