Chapter 10

**Input/Output Interface Circuits and LSI Peripheral Device**

# Lecture Outline

- 10.1 Core and special-purpose I/O interfaces

- 10.2 Byte-Wide output ports using isolated I/O

- 10.3 Byte-Wide input ports using isolated I/O

- 10.4 Input/Output handshaking and parallel printer interface

- 10.5 the 8255 Programmable Peripheral Interface

## **10.1** Core and Special Purpose I/O Interfaces

- <u>Special purpose I/O interfaces</u> are implemented as add-on cards on the PC

- display

- parallel printer interface

- serial communication interface

- local area network interface

- not all microcomputer systems employ each of these types

- <u>Core input/output interfaces</u> are considered to be the part of the I/O subsystem such as:

- parallel I/O to read the settings of the DIP switches on the processor board

- interval timers used in DRAM refresh process

- We will study both

#### **10.2** I/O Design in the 8088/86

- In every computer, when data is sent out by the CPU, the data on the data bus must be latched by the receiving device

- While memories have an internal latch to grab the data on the data bus, a latching system must be designed for ports

- Since the data provided by the CPU to the port is on the system data bus for a limited amount of time (50 -1000ns) it must be <u>latched</u> before it is lost

- Likewise, when data is coming in by way of a data bus (either from port or memory) it must come in through a <u>three-state buffer</u>

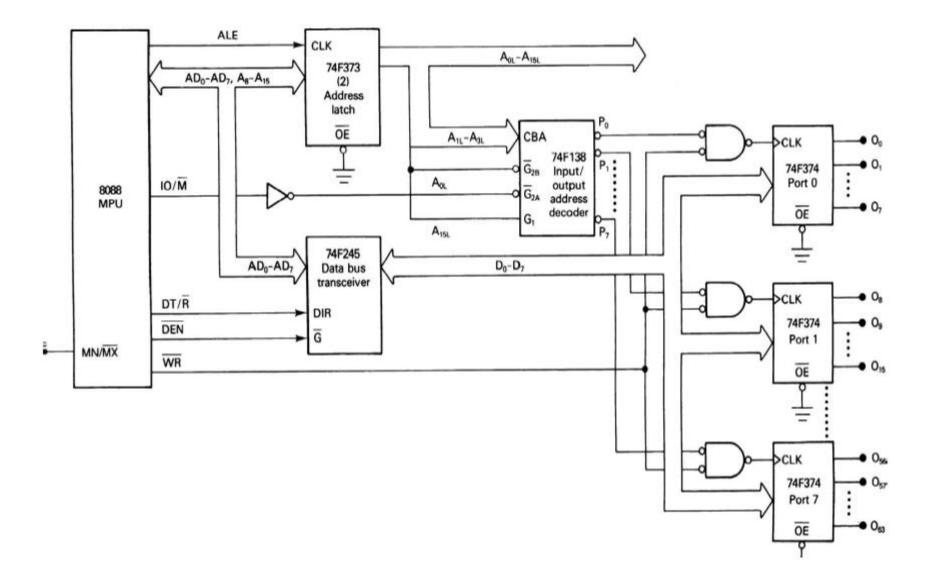

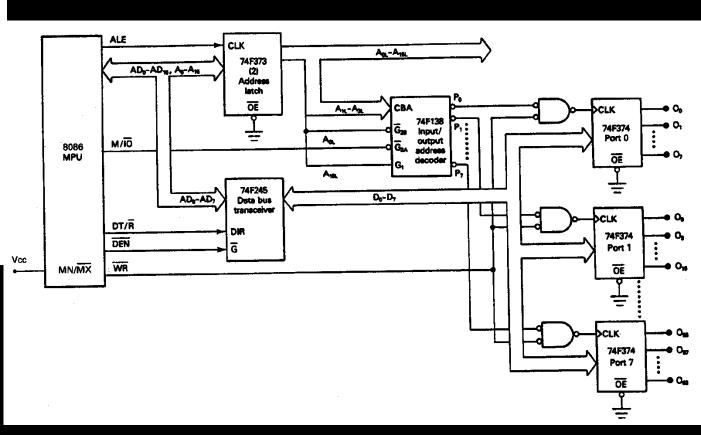

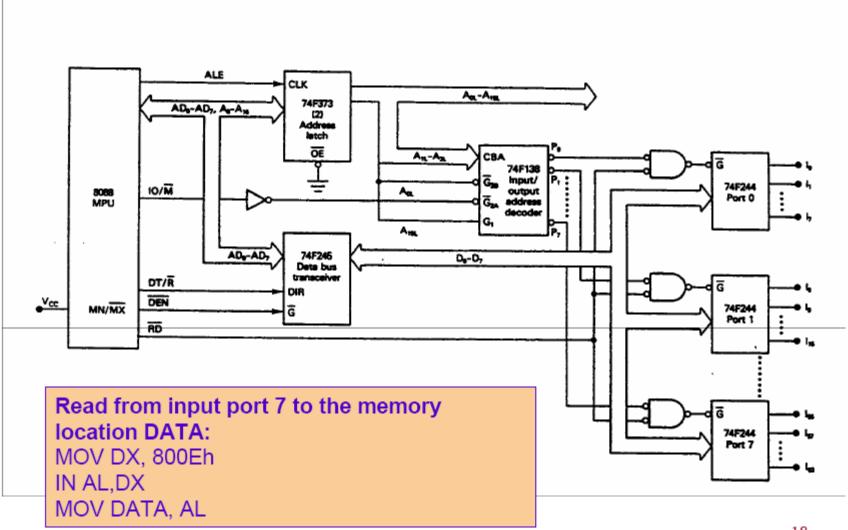

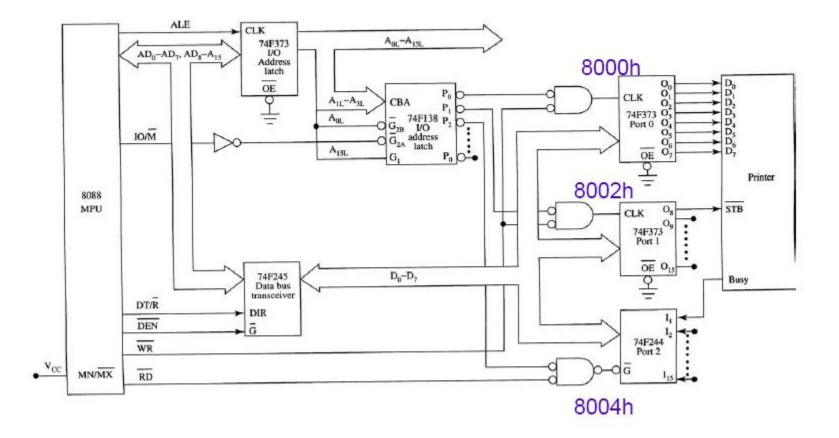

#### Example - 64 line parallel output circuit - 8088

# I/O decoding and the 8086 64-line parallel port

| I/O port | I/O address               |  |

|----------|---------------------------|--|

| Port 0   | 1XXXXXXXXXXX0000          |  |

| Port 1   | 1XXXXXXXXXXX0010          |  |

| Port 2   | 1XXXXXXXXXXX0100          |  |

| Port 3   | 2<br>1XXXXXXXXXX0110      |  |

| Port 4   | 2<br>1XXXXXXXXXX1000      |  |

| Port 5   | 1XXXXXXXXXXX1010          |  |

| Port 6   | 1XXXXXXXXXXX1100          |  |

| Port 7   | 2<br>1XXXXXXXXXX1110<br>2 |  |

|          | · · · · ·                 |  |

#### Examples

- To which output port in the previous figure are data written when the address put on the bus during an output bus cycle is 8002h?

- A15 .. A0 = 1000 0000 0000 0010b

- A15L = 1

- A0L = 0

- A3L A2L A1L = 001

- $-\overline{P1}=0$

- Write a sequence of instructions that output the byte contents of the memory address DATA to output port 0 in the previous figure

MOV DX, 8000h MOV AL,DATA OUT DX, AL

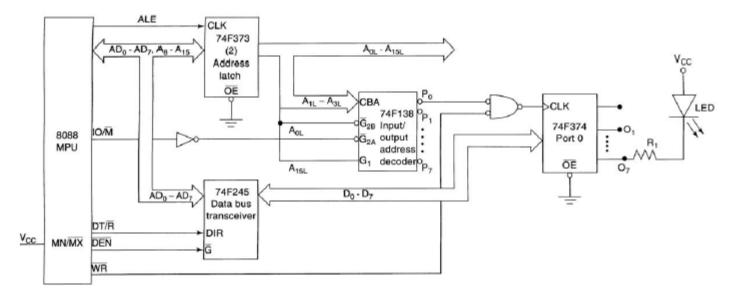

#### Time Delay Loop and Blinking a LED at an Output

Figure 10-2 Driving an LED connected to an output port.

| MOV DX, 8000h<br>MOV AL, 00h<br>ON OFF: OUT DX,AL | ;initialize address of port 0<br>; load data with bit 7 as logic 0<br>; turned on |                                       |

|---------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------|

| MOV CX,0FFFFh                                     | ; load delay count of FFFFh                                                       | Aprox.                                |

| HERE: LOOP HERE                                   | ; complement bit 7                                                                | → 17 T states<br>* 64K *<br>Frequency |

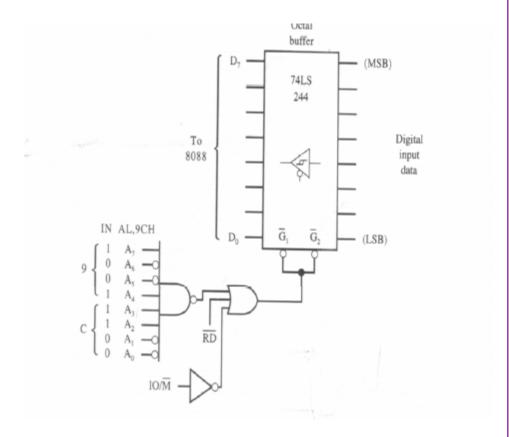

#### **10.3 IN port design using the 74LS244**

#### ➤Design for IN AL,9CH

In order to prevent any unwanted data (garbage) to come into the system (global) data bus, all input devices must be isolated through the tri-state buffer. The 74LS244 not only plays this role but also provides the incoming signals sufficient strength (driving capability) to travel all the way to the CPU

It must be emphasized that every device (memory, peripheral) connected to the global data bus must have a latch or a tri-state buffer. In some devices such as memory, they are internal but must be present.

17

#### Example - 64 line parallel input circuit

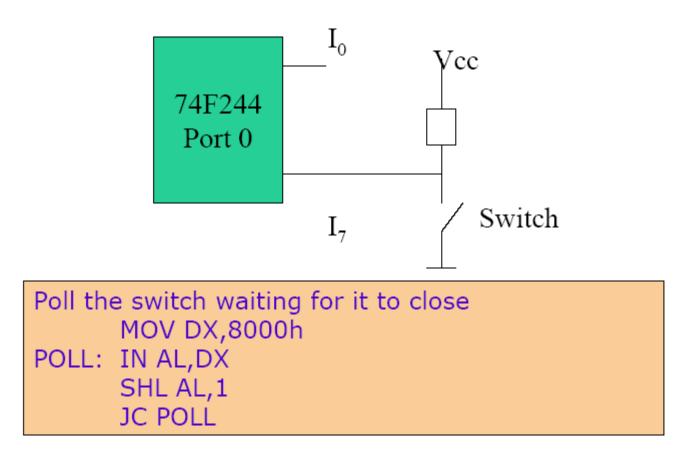

## Example

In practical applications, it is sometimes necessary within an I/O service routine to repeatedly read the value at an input line and test this value for a specific logic level.

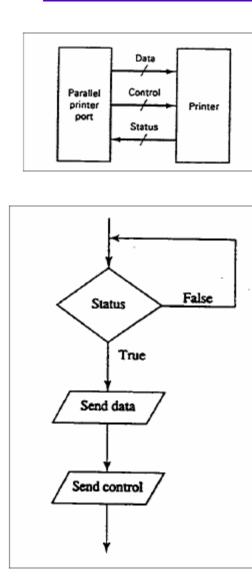

#### **10.4 Input Output Handshaking**

- The I/O ports of a computer typically operate at different data rates

- ➤ A hard disk drive, for example, might require the computer to input data at 10Mbps → 100Mbps

- CD-ROM drives operate at 300-600 Kbps

- However when inputting keystrokes from the operator, the data rate may fall to only one or two characters per sec.

- If the processor is to operate efficiently, one needs to develop a strategy to control or synchronize the flow of data between the processor and the widely varying rates of its I/O devices

- This type of synchronization is achieved by implementing what is known as handshaking as part of the input/output interface

- Printers typically have buffers that can be filled by the computer at high speed

- Once full the computer must wait while the data in the buffer is printed

- Most printer manufacturers have settled on a standard set of data and control signals Centronics Parallel Printer Interface

#### **Parallel Printer Interface**

| Pin | Assignment  |

|-----|-------------|

| 1   | Strobe      |

| 2   | Data 0      |

| 3   | Data 1      |

| 4   | Data 2      |

| 5   | Data 3      |

| 6   | Data 4      |

| 7   | Data 5      |

| 8   | Data 6      |

| 9   | Data 7      |

| 10  | Ack         |

| 11  | Busy        |

| 12  | Paper Empty |

| 13  | Select      |

| 14  | Auto Foxt   |

| 15  | Error       |

| 16  | Initialize  |

| 17  | Sictin      |

| 18  | Ground      |

| 19  | Ground      |

| 20  | Ground      |

| 21  | Ground      |

| 22  | Ground      |

| 23  | Ground      |

| 24  | Ground      |

| 25  | Ground      |

| Data:    | Data0, Data1,, Data7                          |

|----------|-----------------------------------------------|

| Control: | Strobe<br>Auto Foxt<br>Initialize<br>Slctin   |

| Status:  | Ack<br>Busy<br>Paper Empty<br>Select<br>Error |

ACK is used by printer to acknowledge receipt of data and can accept a new character.

**BUSY** high if printer is not ready to accept a new character

SELECT when printer is turned on

ERROR goes low when there are conditions such as paper jam, out of paper, offline

STROBE when PC presents a character

INITIALIZE Clear Printer Buffer and reset control

#### **Operational Principle - Parallel Printer Port**

- The computer checks the BUSY signal from the printer, if not BUSY then

- When the PC presents a character to the data pins of the printer, it activates the STROBE pin, telling it that there is a byte sitting at the data pins. Prior to asserting STROBE pin, the data must be at at the printer's data pins for at least 0.5 microsec. (data setup time)

- The STROBE must stay for 0.5 microsec

- The printer asserts BUSY pin indicating the computer to wait

- When the printer picks up the data, it sends back the ACK signal, keeps ACK low for 5 microsec.

- As the ACK signal is going high, the printer makes the BUSY pin low to indicate that it is ready to accept the next byte

- The CPU can use ACK or BUSY signals from the printer to initiate the process of sending another byte

#### Handshaking

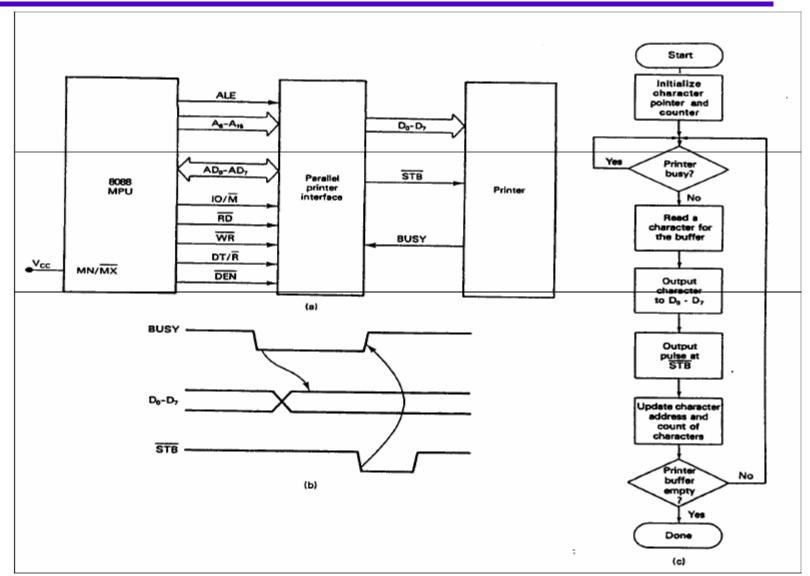

#### **Printer Interface Circuit**

## Example

Write a program that implements the flowchart. Character data is held in memory starting at address PRNT\_BUFF, the number of characters held in the buffer is identified by the count address CHAR\_COUNT.

|            | MOV CL, CHAR_COUNT<br>MOV SI, OFFSET PRNT                                                                                   |                                      |                                           |

|------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------|

| POLL_BUSY: | MOV DX,8004h<br>IN AL,DX<br>AND AL,01h<br>JNZ POLL_BUSY<br>MOV AL, [SI]<br>MOV DX,8000h<br>OUT DX,AL                        |                                      | BUSY input checked<br>Character is output |

|            | MOV AL, 00h<br>MOV DX,8002h<br>OUT DX,AL<br>MOV BX,0Fh<br>STROBE: DEC BX<br>JNZ STROBE<br>MOV AL,01h<br>OUT DX,AL<br>INC SI | ;STB = 0<br>; delay for<br>; STB bar |                                           |

|            | DEC CL<br>JNZ POLL_BUSY                                                                                                     |                                      |                                           |

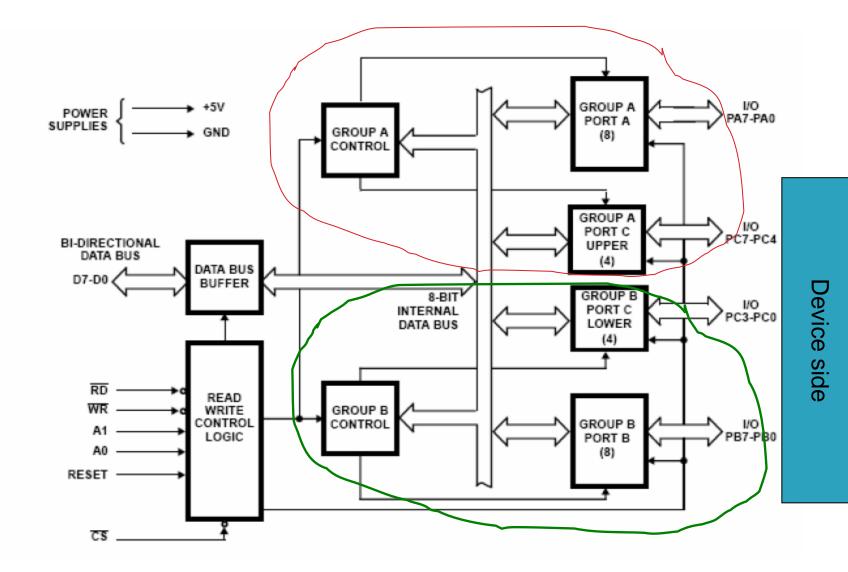

#### **10.5**The 8255 Programmable Peripheral Interface

- Intel has developed several peripheral controller chips designed to support the 80x86 processor family. The intent is to provide a complete I/O interface in one chip.

- 8255 PPI provides three 8 bit input ports in one 40 pin package making it more economical than 74LS373 and 74LS244

- The chip interfaces directly to the data bus of the processor, allowing its functions to be programmed; that is in one application a port may appear as an output, but in another, by reprogramming it as an input. This is in contrast with the 74LS373 and 74LS244 which are hardwired and fixed

- Other peripheral controller chips include the 8259 Programmable Interrupt Controller (PIC), the 8253/54 Programmable Interval Timer (PIT) and the 8237 DMA controller

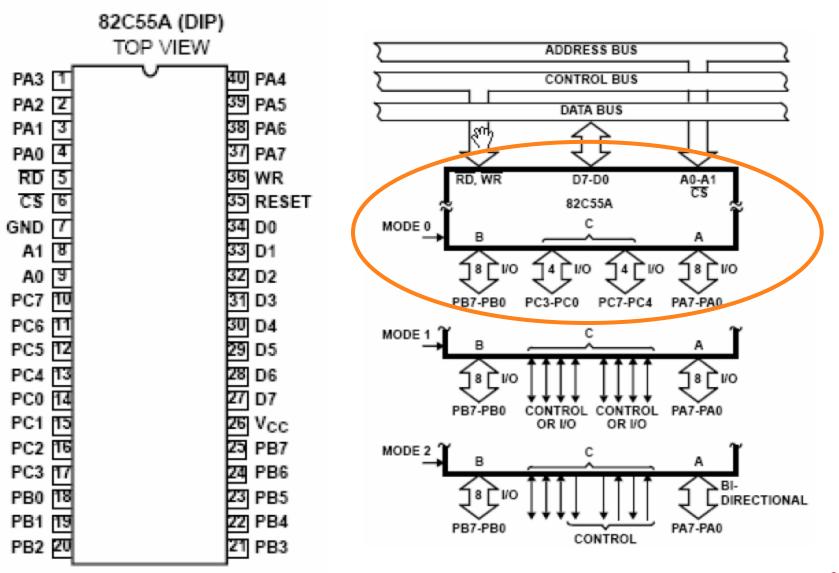

#### 8255A internal

Processor -side

31

#### 8255 Pins

- PA0 PA7: input, output, or bi-directional port

- PB0 PB7: input or output

- PC0 PC7: This 8 bit port can be all input or output. It can also be split into two parts, CU (PC4 - PC7) and CL (PC0 - PC3). Each can be used for input and output.

- RD or WR

- IOR and IOW of the system are connected

- RESET

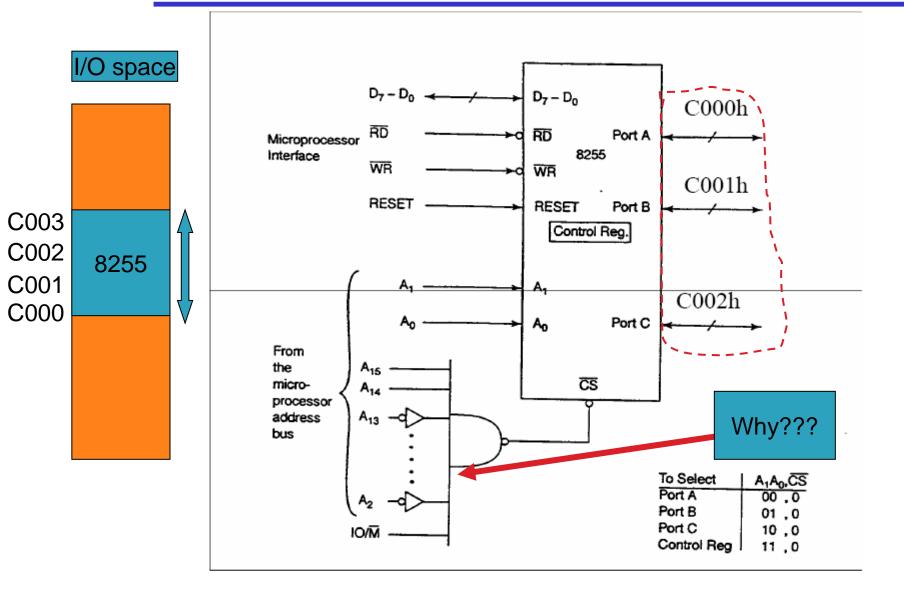

- A0, A1, and CS

- CS selects the entire chip whereas A0 and A1 select the specific port (A, B, or C)

| CSBAR | A1 | A0 | SELECTS:          |

|-------|----|----|-------------------|

| 0     | 0  | 0  | Port A            |

| 0     | 0  | 1  | Port B            |

| 0     | 1  | 0  | Port C            |

| 0     | 1  | 1  | Control Register  |

| 1     | х  | Х  | 8255 not selected |

| -        | ٦ |       |      |

|----------|---|-------|------|

| 🗖 1 PA3  | ~ | PA4   | 40 🗆 |

| 2 PA2    |   | PA5   | 39 🗖 |

| 🖾 3 PA1  |   | PA6   | 38 🗖 |

| 4 PA0    |   | PA7   | 37 🗖 |

| 5 RD     |   | WR    | 36 🗖 |

| 🗆 6 CS   |   | RESET | 35 🗖 |

| T 7 GND  | • | DO    |      |

| 🗖 8 A1   | 8 | D1    | 33 🗖 |

| 🗖 9 A0   | 2 | D2    | 32 🗖 |

| 10 PC7   | 5 | D3    | 31 🗖 |

| 11 PC6   | - | D4    | 30 🗖 |

| 12 PC5   | 5 | D5    | 29 🗖 |

| 13 PC4   | Α | D6    | 28 🗖 |

| 🗖 14 PC0 |   | D7    | 27 🗖 |

| 15 PC1   |   | Vcc   | 26 🗖 |

| 16 PC2   |   | PB7   | 25 🗆 |

| 17 PC3   |   | PB6   | 24 🗆 |

| 18 PB0   |   | PB5   | 23 🗆 |

| 19 PB1   |   | PB4   | 22 🗆 |

| 🗖 20 PB2 |   | PB3   | 21 🗆 |

|          |   |       |      |

ure 11-11 8255 PPI Chin

#### Addressing an 8255

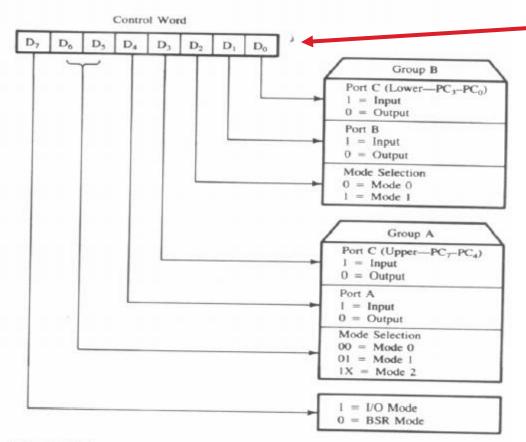

#### 8255 Control Word Format

#### **Control register**

#### FIGURE 15.4

8255A Control Word Format for I/O Mode

SOURCE: Adapted from Intel Corporation, Peripheral Components (Santa Clara, Calif.: Author, 1993), p. 3-

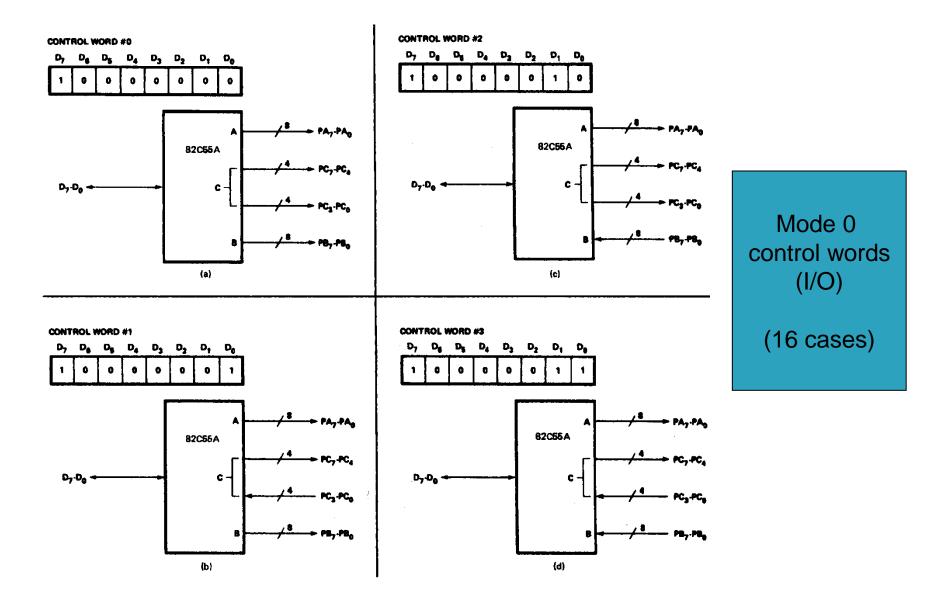

## Mode 0 - Simple input/output

- Simple I/O mode: any of the ports A, B, CL, and CU can be programmed as input or output.

- Example: Configure port <u>A as input</u>, <u>B as output</u>, and all the bits of port <u>C</u> as output assuming a base address of 50h

- Control word should be 1001 0000b = 90h

PORTA EQU 50h PORTB EQU 51h PORTC EQU 52h CNTREG EQU 53h MOV AL, 90h OUT CNTREG,AL IN AL, PORTA OUT PORTB, AL OUT PORTC, AL

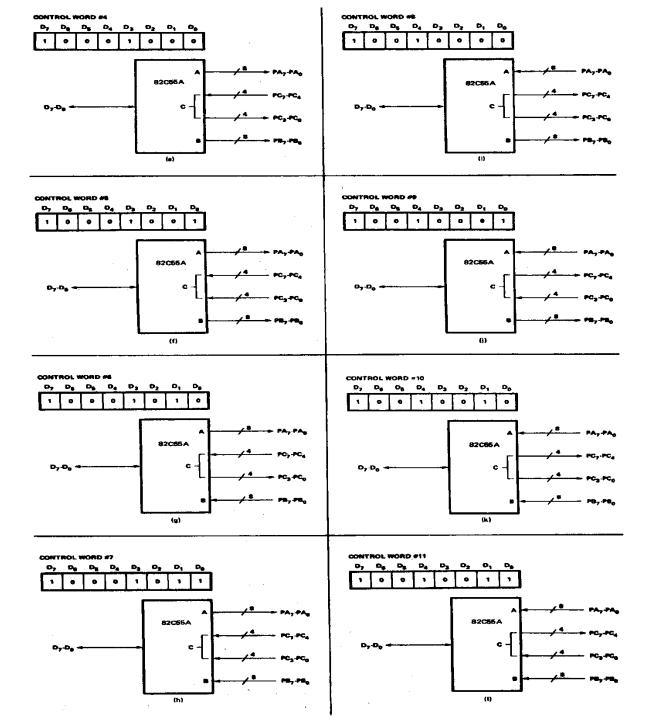

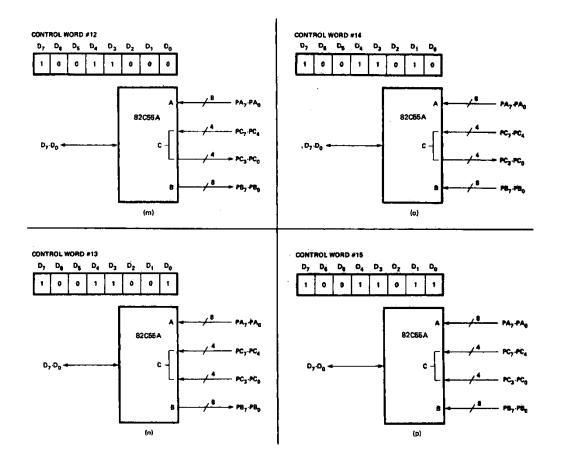

#### Mode 0 control words (I/O)

#### Mode 0 control words (I/O)

## Mode 1: I/O with Handshaking Capability

- Handshaking refers to the process of communicating back and forth between two intelligent devices

- Example: Process of communicating with a printer

- a byte of data is presented to the data bus of the printer

- the printer is informed of the presence of a byte of data to be printed by activating its strobe signal

- whenever the printer receives the data it informs the sender by activating an output signal called ACK

- the ACK signal initiates the process of providing another byte of data to the printer

- 8255 in mode 1 is equipped with resources to handle handshaking signals

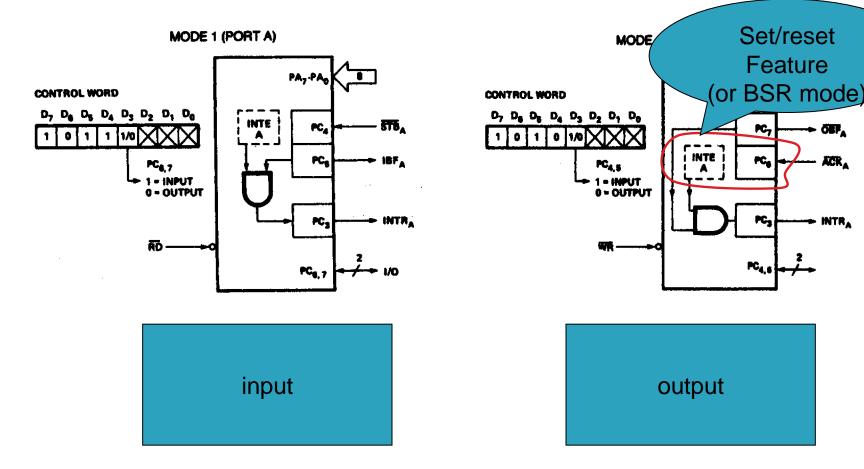

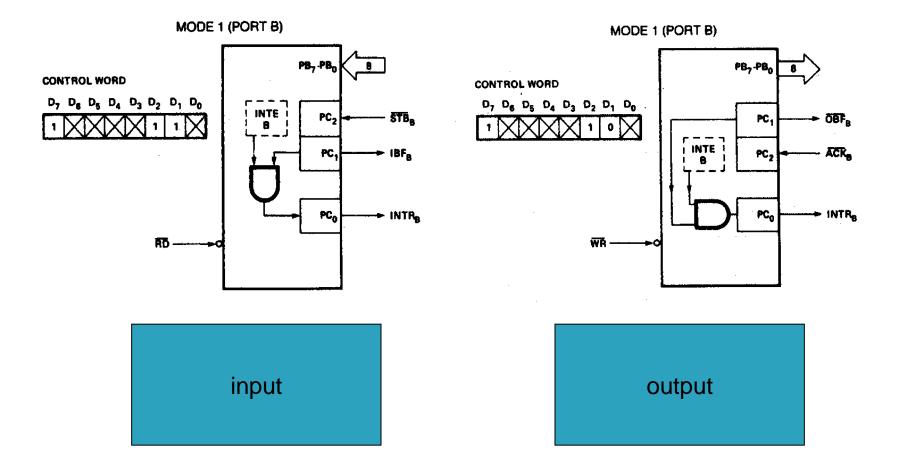

# Setup of Mode 1

|                                    | MODE 1            |                   |  |

|------------------------------------|-------------------|-------------------|--|

| Pin                                | IN                | OUT               |  |

| PA <sub>0</sub>                    | IN                | OUT               |  |

| PA <sub>1</sub>                    | IN                | OUT               |  |

| PA <sub>2</sub>                    | IN                | OUT               |  |

| PA₃<br>PA₄<br>PA₅                  |                   | OUT<br>OUT<br>OUT |  |

| PA <sub>6</sub>                    | IN                | OUT               |  |

| PA <sub>7</sub>                    | IN                | OUT               |  |

| PB <sub>0</sub>                    | IN                | OUT               |  |

| PB <sub>1</sub>                    | IN                | OUT               |  |

| PB <sub>2</sub>                    | IN                | OUT               |  |

| PB₃                                | IN                | OUT               |  |

| PB₄                                | IN                | OUT               |  |

| PB₅                                | IN                | OUT               |  |

| PB <sub>6</sub><br>PB <sub>7</sub> | IN<br>IN          |                   |  |

| PC <sub>0</sub>                    | INTR <sub>B</sub> | INTR <sub>B</sub> |  |

| PC <sub>1</sub>                    | IBF <sub>B</sub>  | OBF <sub>B</sub>  |  |

| PC <sub>2</sub>                    | STB <sub>B</sub>  | ACK <sub>B</sub>  |  |

| PC <sub>3</sub>                    | INTR <sub>A</sub> | INTR <sub>A</sub> |  |

| PC <sub>4</sub>                    | STB <sub>A</sub>  | I/O               |  |

| PC <sub>5</sub>                    | IBF <sub>A</sub>  | I/O               |  |

| PC <sub>6</sub>                    | I/O               | ACK <sub>A</sub>  |  |

| PC <sub>7</sub>                    | I/O               | OBF <sub>A</sub>  |  |

# Mode 1 (configuration of port A)

+ ÖFF\_

ACR\_

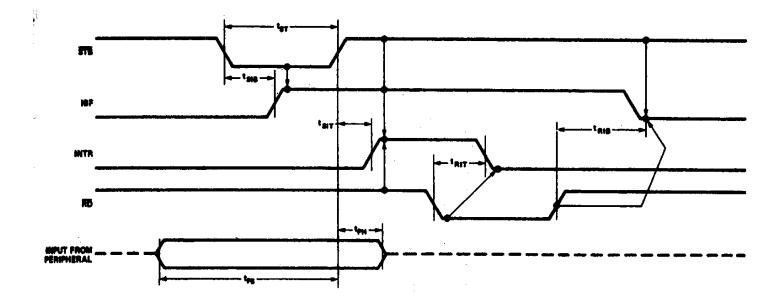

# Timing diagram of port A (input)

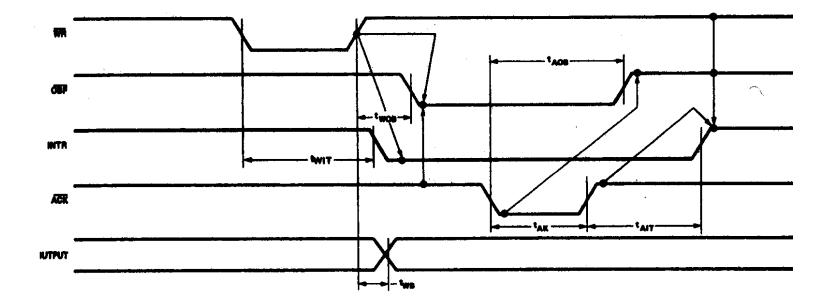

# Timing diagram of port A (output)

## Mode 1 (configuration of port B)

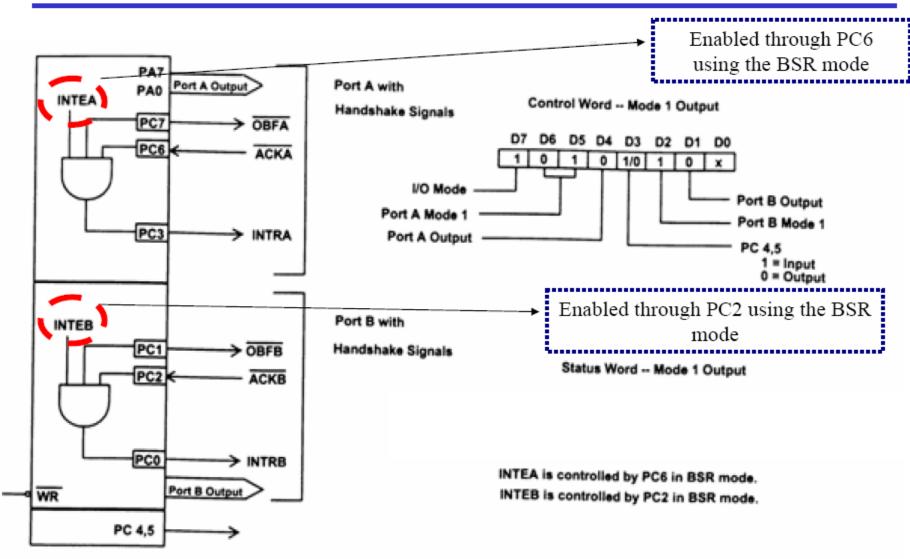

#### Mode 1 Strobed Output

## Mode 1 Strobed Output Signals

- OBFa (output buffer full for port A)

- indicates that the CPU has written a byte of data into port A

- must be connected to the STROBE of the receiving equipment

- Goes back high again after ACK'ed by the peripheral.

- ACKa (acknowledge for port A)

- through ACK, 8255 knows that data at port A has been picked up by the receiving device

- 8255 then makes OBFa high to indicate that the data is old now. OBFa will not go low until the CPU writes a new byte of data to port A.

- INTRa (interrupt request for port A)

- it is the rising edge of ACK that activates INTRa by making it high.

INTRa is used to get the attention of the microprocessor.

- it is important that INTRa is high only if INTEa, OBFa, ACKa are all high

- it is reset to zero when the CPU writes a byte to port A

- The 8255 enables the monitoring the status signals INTR, OBF, and INTE for both ports A and B. This is done by reading port C into the accumulator and testing the bits. This feature allows the implementation of polling

## Mode 1 Input Ports with Handshaking Signals

- STB

- When an external peripheral device provides a byte of data to an input port, it informs the 8255 through the STB pin. STB is of limited duration

- IBF (Input Buffer Full)

- In response to STB, the 8255 latches into its internal register the data present at PA0-PA7 or PB0-PB7.

- Through IBF it indicates that it has latched the data but it has not been read by the CPU yet

- To get the attention of the CPU, IBF activates INTR

- INTR

- Falling edge of RD makes INTR low

- The RD signal from the CPU is of limited duration and when it goes high the 8255 in turn makes IBF inactive by setting it low

- IBF in this way lets the peripheral know that the byte of data was latched by the 8255 and read into the CPU as well.

- The two flip flops INTEA and INTB are set/reset using the BSR mode. The INTEA is enabled or disabled through PC6 and INTEB is enabled or disabled through PC2.

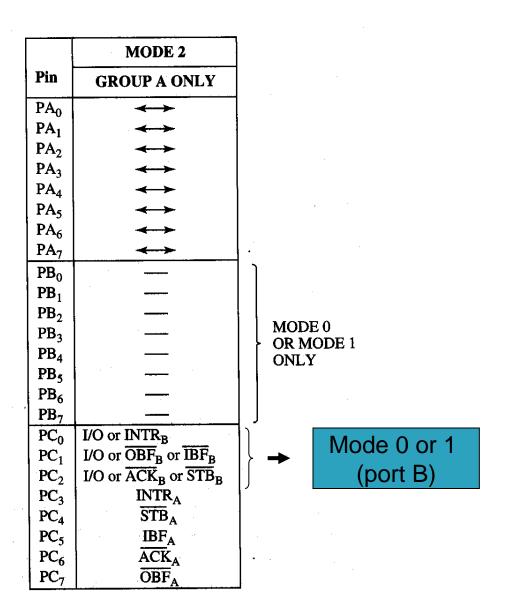

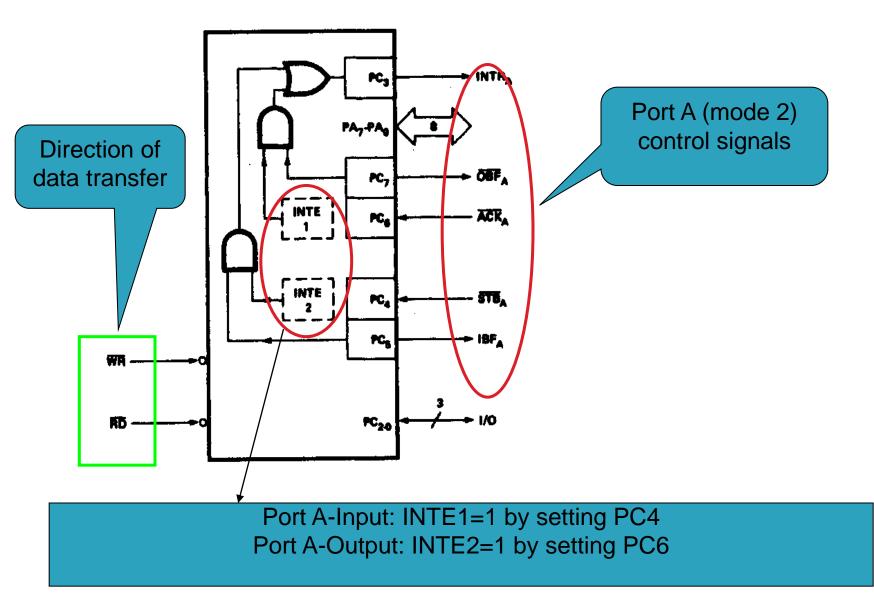

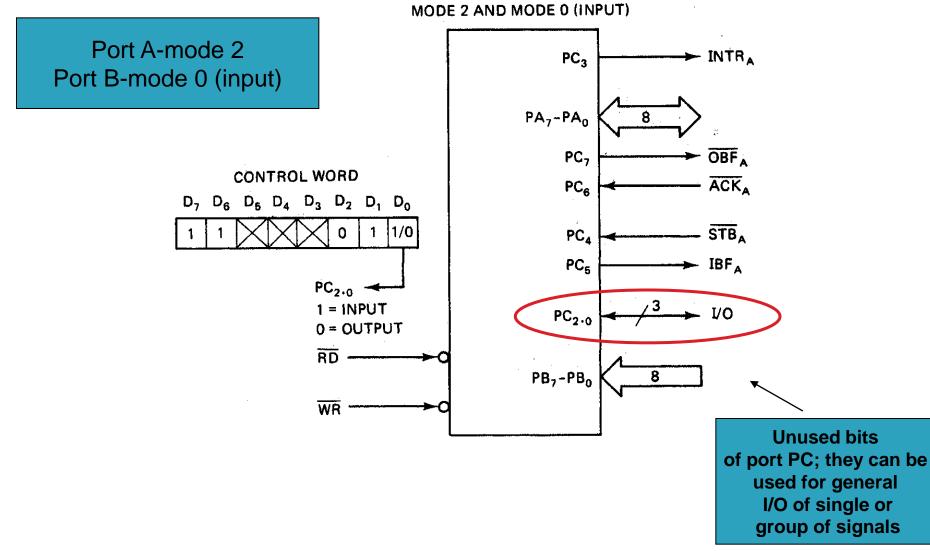

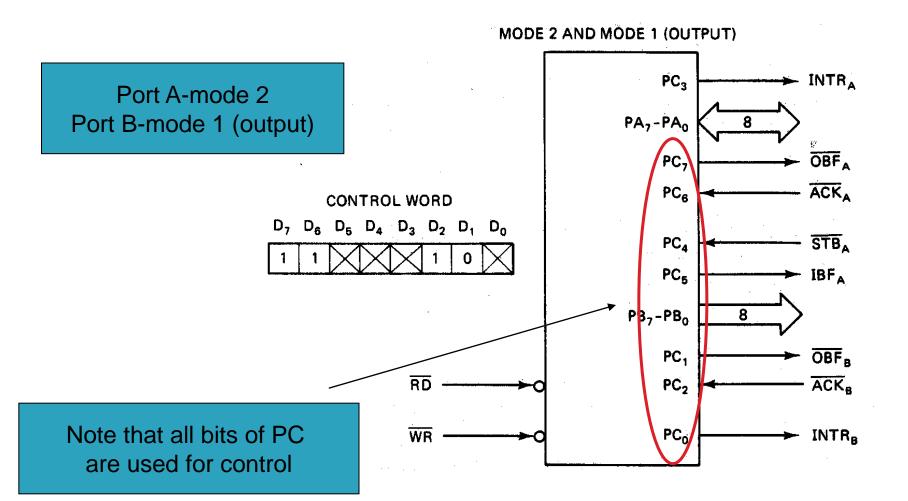

#### Mode 2 Strobed Bidirectional I/O

- In this Mode Port A is A bidirectional I/O port

- Port C Provide the control functions for both directions

- To select this Mode D7 and D8 of the control register should be 1's (i.e. 11XXXXX).

# Setup of Mode 2

#### Mode 2 (configuration of port A)

# **Combined Modes**

# Combined Modes (cont'd)

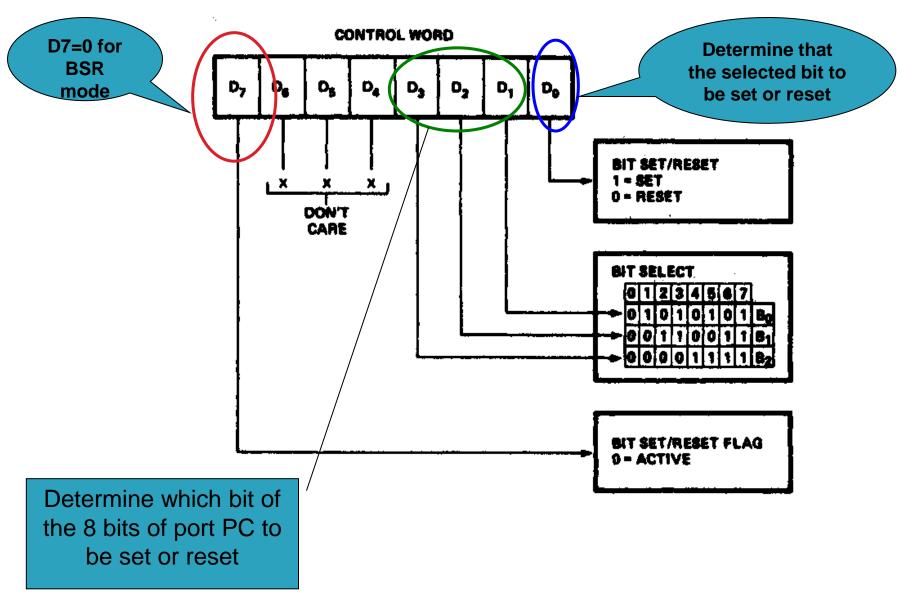

## Bit set/reset Mode (BSR mode)

# Example 1: BSR mode

The interrupt control flag INTEA for port A is controlled by PC6. Using te BSR mode of 8255A. What configuration code must be written to the control register to set it to enable this control flag?

#### Solution:

- 1. D7=0

- 2. INTEA is to be set, hence, D0=1

- 3. To select PC6 then D3 D2 D1=110.

- 4. The remaining bits are don't care.

So.....

Control register=0XXX1101 or 00001101.

## Example 2: BSR mode

Assume that the 8255 is mapped to the address 0080H in the I/O space:

≻Ex: Write a BSR word subroutine to set PC7 and PC3

To Set PC7  $\rightarrow$  OFH ; To set PC3  $\rightarrow$  07H

MOV AL,0FH OUT 83H,AL MOV AL,07H OUT 83h,AL

Note that we sent two different control words to the control register to set, respectively, PC7 and PC3.

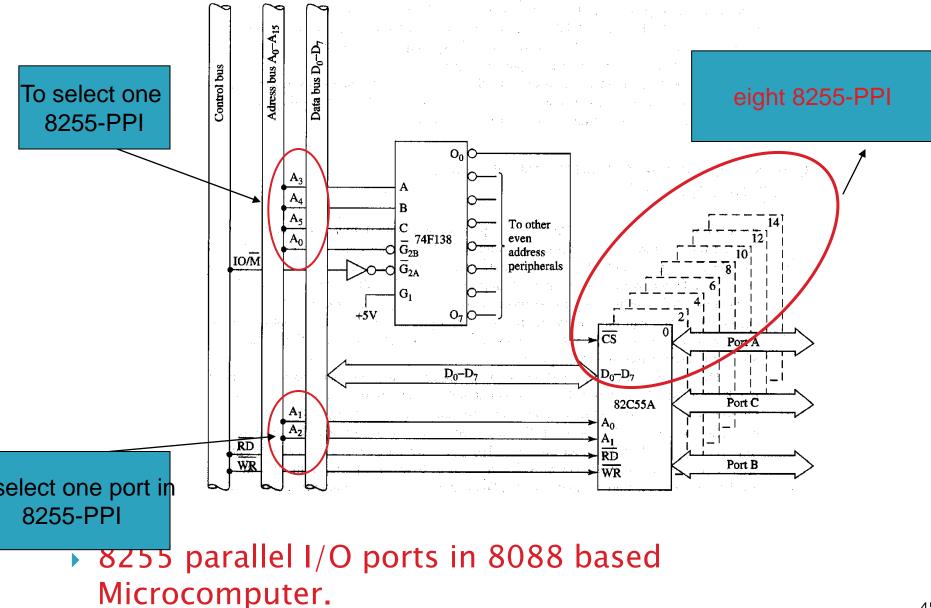

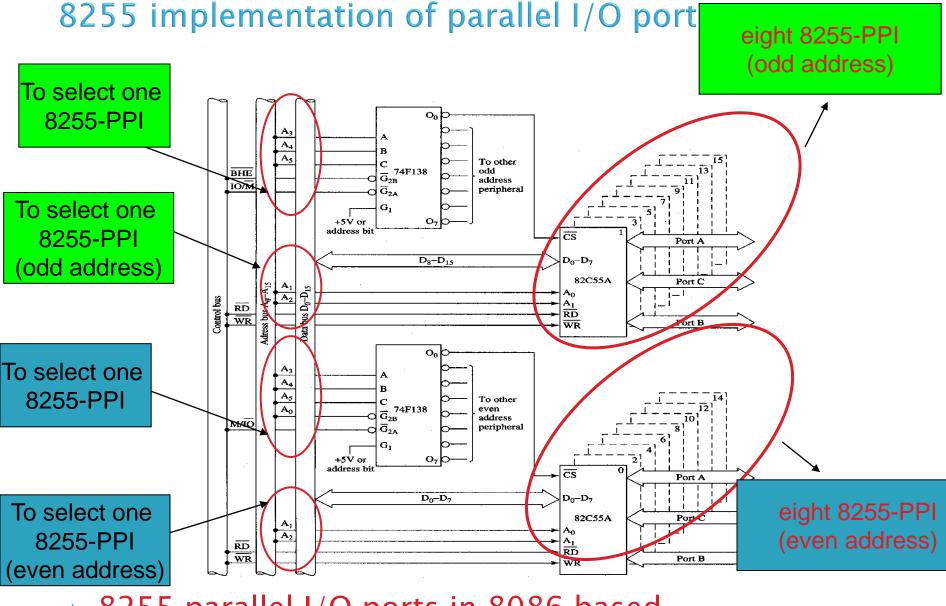

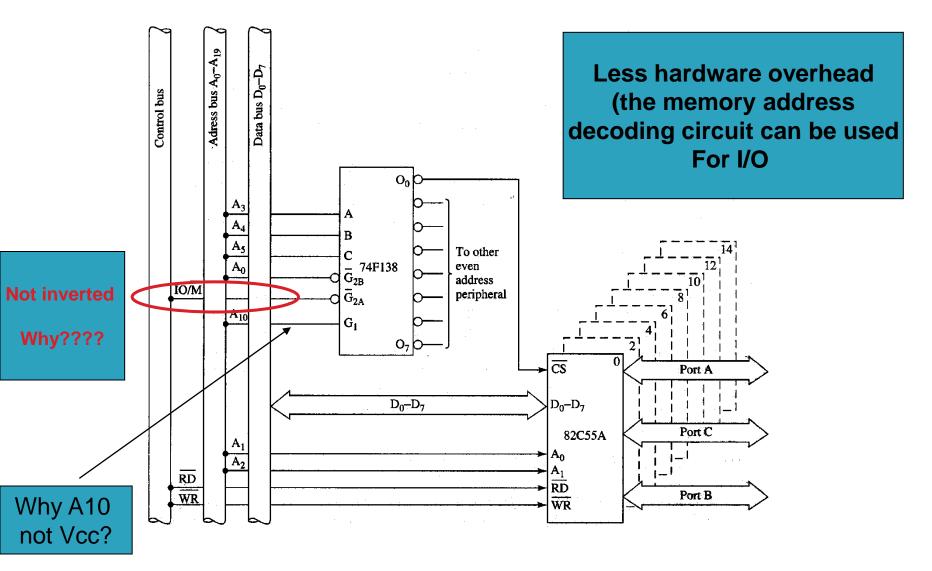

#### 8255 implementation of parallel I/O ports

8255 parallel I/O ports in 8086 based Microcomputer.

## Example 1:

- What must be the address bus inputs of the circuit shown in Fig 10.21 if port C of PPI 14 is to be accessed?

- Answer:

- 1. To enable PPI 14, the decoder 74138 must be enabled and O7 must be 0 (active), G2B=0 and CBA=111.

- 2.  $A_0=0$  to enable decoder (74138) and  $A_5A_4A_3=111$

- 3. Port C of PPI is selected A1A0=10 or (A2A1=10 from the bus)

- 4. The rest of addresses are don't care

## Example 2:

- Assume that PPI 14 of Fig 10.21 is configured so that Port A is output and C and B are inputs. All in mode 0. Write a program that input data from ports C and B and then find the difference between C and B (PC-PB) and then output it to port A ?

- Answer:

- 1. To enable PPI 14, the decoder 74138 must be enabled and

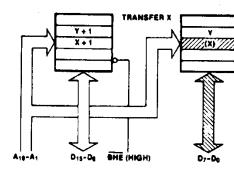

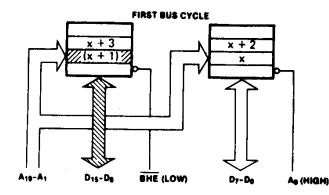

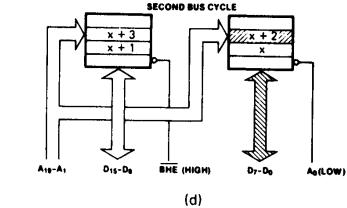

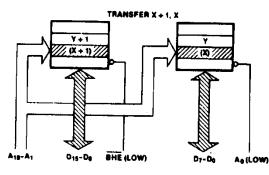

#### Memory-processor data transfer

Ap (HIGH)

Misaligned word

.

As (LOW)

(c)

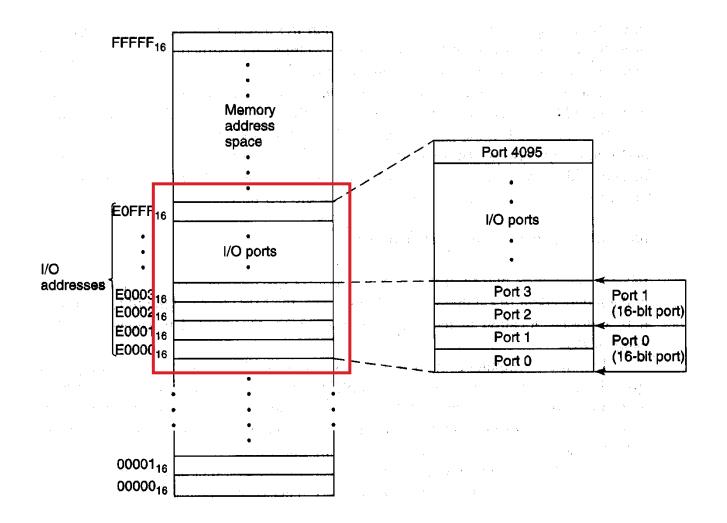

# Memory mapped I/O

- I/O devices can be mapped to the memory address space.

- MPU looks at the I/O port as a storage location in memory.

- In micro-computer with M-M I/O, some memory addresses are dedicated for I/O port.

- Advantages:

- Instruction that affect data in memory are used for I/O instead of special I/O instruction.

- Hence, much more instructions and addressing modes are available for I/O operation.

- For example data transfer can be performed not only with AL and AX but also with the other internal registers.

- Disadvantages:

- Slower operations than those specially designed for I/O

- Part of memory space is lost.

## Memory-mapped I/O

#### Memory-mapped I/O

# Example 1 for M-M I/O:

- Which I/O port in Fig 10.23 is selected for operation when Memory address bus contains 00402H

- Answer:

- 1. Convert to binary: 000000000100000010

- 2. Then, we find, A10=1 and A0=0 and IO/Mprime=0 (memory operation)

- 3. Now, A5A4A3=000, then PPI 0 is selected

- 4. Moreover, A2A1=01, then Port B of PPI 0 is selected.

# Example 2 for M–M I/O:

- Write a sequence of instruction to initialize the control register of PPI 0 in Fig 10.23 so Port A is output and ports B and C are inputs, all ports in mode 0.

- Answer:

- 1. Control register=10001011=8BH

- 2. Memory address of PPI0=000000001000000110=00406

- 3. **Code:**

MOV AX, 0 MOV DS, AX MOV AL, 8BH MOV [406H], AL

## Example 3 for M–M I/O:

- Assume the same configuration of Example 2. Write a sequence of instruction so that the content of B and C are ANDED then output the result to port A.

- Answer:

- Address of the ports: address port A=00400, address port B=00402, and address port C=00404.

- 2. **Code**:

MOV AX, 0 MOV DS, AX MOV AL, 8BH MOV [406H], AL MOV BL, [402H] MOV AL, [404H] AND AL, BL MOV [400H], AL