# معالجات ومتحكمات دقيقة

د.محمد عبابنة

الطالب المبدع محمد زغول

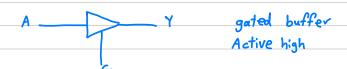

Allows info to go from A to Y

based an info from G

in the case of Active high, A goes to

Y if G is 1 (high), whereas in Active

low, A goes to Y if G is 0 (low).

A G Y

1 1 1 Kilobyte

$$\rightarrow 2^{16}$$

0 1 0 megabyte  $\rightarrow 2^{26}$

X 0 hi-Z gigabyte  $\rightarrow 2^{30}$

high impedance terabyte  $\rightarrow 2^{40}$

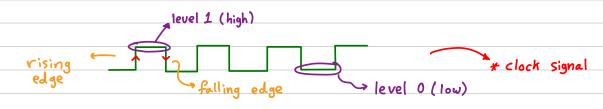

Instruction cycles = 4 Tclk

ex:  $CLR \rightarrow 1$ Self  $\rightarrow 1$ goto  $L_1 \rightarrow 2$ Self port  $A \rightarrow 1$

| Numbering      | systems           | bit                                  |

|----------------|-------------------|--------------------------------------|

| 1 Binar        | ry number (o-1)   | nibble = 4 bits                      |

| ② decim        | al number (0-9)   | byte = 8 bits                        |

| 3 octal        | number (o-7)      | word = 16 bits                       |

| (1) hexad      | ecimal (0-9)(A-F  |                                      |

| 1,             |                   |                                      |

| * How to co    | nvert from binary | to Hexadecima                        |

|                | L Hex number ta   | kes 4 bits                           |

|                | 8421              | 8421                                 |

|                | (110 111110       | $\frac{8421}{1110}_{2} = (37EE)_{H}$ |

|                |                   |                                      |

| <u>Decimal</u> | Binary            | Hexadecimal (H)                      |

| 0              | 0000              | 0                                    |

| 1              | 0001              | 1                                    |

| 2              | 0010              | 2                                    |

| 3              | 0011              | 3                                    |

| Ч              | 0   0 0           | Ч                                    |

| 5              | 0101              | 5                                    |

| 6              | 0110              | 66                                   |

| 7              | 0111              | 7                                    |

| 8              | 1000              | 8                                    |

| 9              | 1001              | 9                                    |

| (0             | 1010              | A                                    |

| 11             | 1011              | В                                    |

| 12             | 1100              | <u>C</u>                             |

| 13             | 1101              | D                                    |

| 14             | 1110              | E                                    |

| 15             | [1 1 ]            | F                                    |

|                |                   |                                      |

```

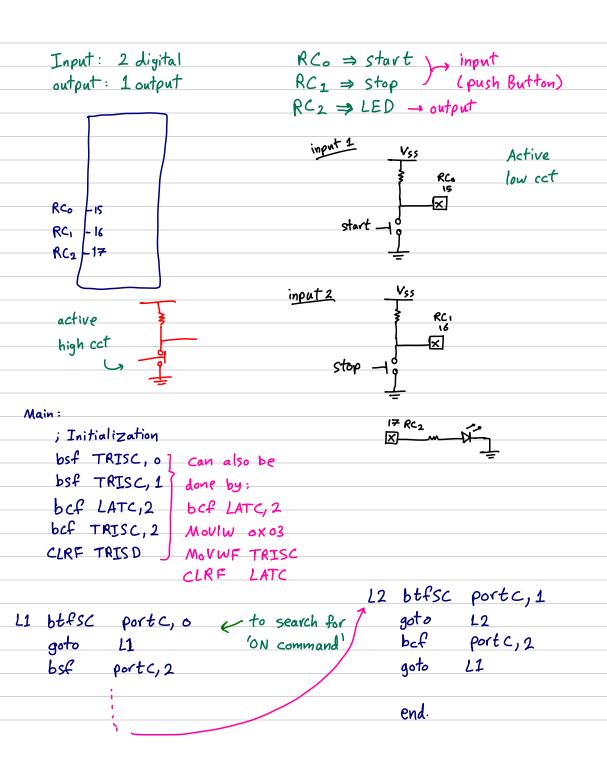

I/o \rightarrow input/output ports

Tris registers

> configures the pins as input or output

(1 \rightarrow input, 0 \rightarrow output)

Lat registers

> Connects the output pins to high or low voltage

(1 - Vdd, 0 - Vss) ground

port registers

> Reads the state of the pins

(1-Vy, o -> Vss)

\rightarrow There are 5 ports (A-E)

* EX: CLRF TRISA

→ TRISA = OX,00

* This way, we defined all

pins on port A (Ao-Az) to be

output

· port A ⇒ 7 bit (Ao -Ac)

SETE TRISA

· port B ⇒ 8 bit (Bo - Bz)

TRISA = oxFF

• port ( ⇒ 8 bit (C0-C7)

Ao-70 are inputs

• port D \Rightarrow 8bit (D_0 - D_2)

bef TRISA, 3

· port E => 3 bit (€0-E2) bit clear file $\frac{1}{2} \land \land

(Ao-Az) input

Az output

to Read the new value on the port

(Ay-AZ) input

bsf TRISB, 2

```

movf portB, o , Read the information and put it in the WREG

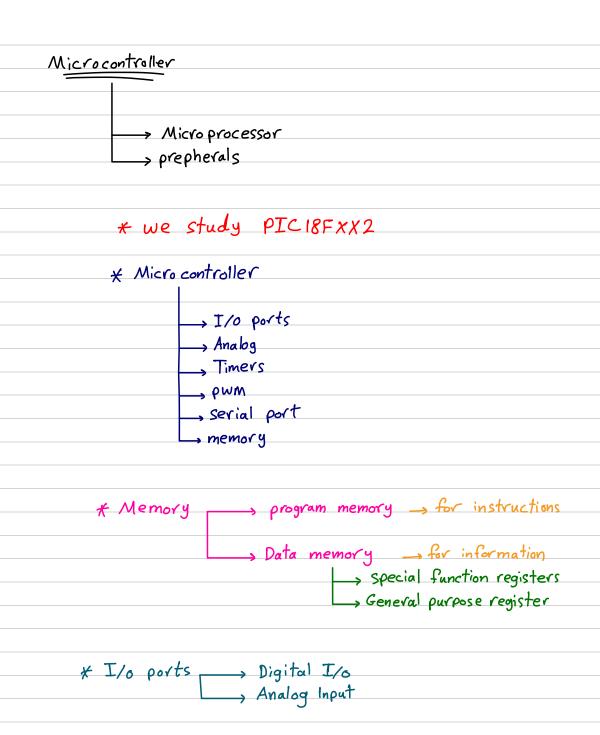

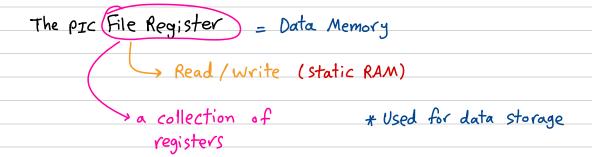

DATA RAM has General Purpose RAM (GPR)

Special Function Registers (SFRs)

SFRs are fixed and must-have, GPR's size is what varies and changes the RAMS size.

\* ROM is used to store the program

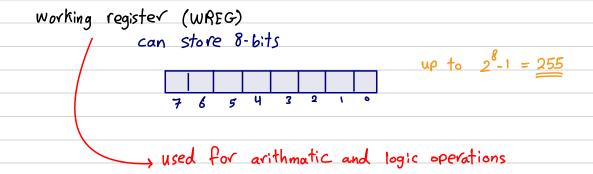

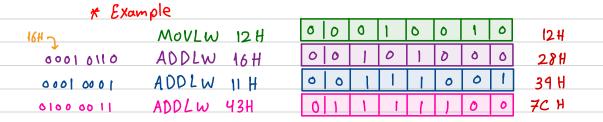

MOVLW

6 moves 8-bit data into the working register

MOVLW X size of x must be 8-bit MOVLW 25H

Hexadecimal

## ADDLW

## GADD literal value K to WREG (K+WREG)

ADDLW  $k \Rightarrow$  takes the value stored in the WREG and adds k to that value then stores the resault back in the WREG

\* After running the above code/instruction what's the value stored in the WREG? -> 7CH

200000h

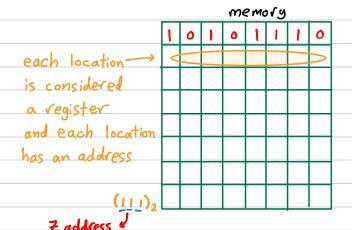

3 address lines / bits - number of bits i need to represent the last address location.

## Special Function Registers

locations

La bunch of registers inside the data memory.

\* specific functions as timers, I/o ports, sevial communication..etc.

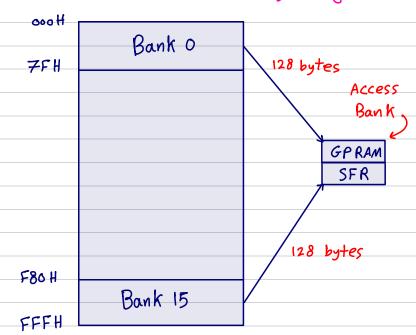

The file register in PIC18 has maximum 4096 212 = 4096 bytes byte (4k), which has addresses 000-FFFH locations) which is divided by banks, each bank has 256 bytes

\* There is at least 1 bank called the access bank which is the default bank.

\* How can we access all banks? by a method called Bank switching

\* The 256-byte access bank is divided by 2 equal sections of 128 bytes

\* Using instructions with the default access bank

(to access other locations in the file register for ALU

and other operations

## MOVWF

tells the cpu to copy the source register (WREG) to a destination in the file register

MOVWF address

Can be in SFR or GPRAM

the address of the destination

| * Example                     | WREG       | Addvess  | Data   |  |

|-------------------------------|------------|----------|--------|--|

| MOVLW 99H                     |            | 012 H    |        |  |

| copies the contents MOVWF 12H | वव भ       | 013 H    |        |  |

| of WREG to a MOVLW 85H        |            | 614 H    |        |  |

| File register that MOVWF 13H  | 85H        | 015 H    | •      |  |

| has address 12H MOVLW 3FH     |            |          | empty) |  |

| MOVWF 14H                     | 3FH        |          |        |  |

| MOVLW 63H                     |            | _Addvess | Data   |  |

| MOVWF 15H                     | <i>63H</i> | 012 H    | 99 H   |  |

|                               |            | 013 H    | 85 H   |  |

| * Note: we cannot move liter  | ral values | 614 H    | 3FH    |  |

| (numbers) directly into the   |            | 015 H    | 63 H   |  |

| RAM location it must be more  | •          |          |        |  |

## ADDWF

6 Adds together the content of WREG and a file register location

\* takes two parameters: Address, D

from Register File

D → 0, w or not specified → WREG

Result will be saved in WREG

1, F → address

Result will be saved in the same address

\* Example: What are the contents of the WREG after running the following program

| 00H E12H3 = 00H        |

|------------------------|

| OOH { 12H3 = 00H       |

| 22H {12H} = 00H        |

| 22H { 12H} : 22H       |

| 22H { 12H}= 44H        |

| 22H <u>{ 12H}= 66H</u> |

| 2H {  2H} = 88H        |

| 2                      |

contents of WREG

after each instruction

COMF

Complements the contents of file register and places the result in WREG

COMF address, D = 1, F

\* Example: write a simple program to toggle the SFR of portB continuosly forever.

MOVLW 55H

MOVWF PORTB , copies 55H from WREG to portB

B1 COMF PORTB, F

Will go to this line

(that has the B1 label)

\* portB is just an address bocation that has a name, its address is F81H so we can also do MOVWF F81H which would be the same.

complement the contents of portB

if was

olololol

then becomes

lolololo and gets

stored in the File register (portB itself)

## MOVF

MOVF address, D

D=0: copies the contents of file register (from I/o pin) to wrece

D=1: The content of file register is copied to itself

\* Example: write a simple program to get data from the SFRs of portB and send it the SFRs of portC continuously

AGAIN MOVF PORTB, W

MOVWF PORTC

GOTO AGAIN

\* To move values from port A to port B

1) MOVFF portA, port B

or→ 10 MOVF portA, w MOVWF portB

\* weak pull-up only available \* it's better to clear the LAT in port B before defining any output incase (which means internally there is it has anything from a previous a current limiting resistor) file. active SFR ⇒ INTCON2 bcf INTCON2, 7 → Initialization RB3 ⇒ Input → start Main: ; Initialization RBs => Input -> stop RBZ > output -> LED bsf TRISB,3 bsf TRISB,5 we will use weak pull-up bcf LATB, 7 bef TRISB, 7 CLRF TRISD L1 btfss port B, 2 goto L1 bsf portB,7 L2 btfss port B,5 goto L2 active High bef port B, 7 buttons goto LI end.

T.C 2 assume for = IMHz delay Taik = IMS Moviu N Movwf count TIC = 4 Tak = 4 MS L2 decfSZ count (N-1)\*1+3goto L2 (N-1) \* 2 128 64 32 16 8 4 2 1 Νορ Return 3N+7 maximum value of N can be 256 : No I.C = 775 Trotal = No. I. C + TI.c = 3.1 mS but what if we want to delay more? we can add another loop I.C delay Movlw M Movf count 2 L3 MOVIW N Movwf count M=2\* M-1 N= 2 L2 decfs= count (N-1)\*1+3(N-1) +2 goto L2 M = 1 decfsz count2 (M-1)\*1+3goto L3 (M-1)\*2Return

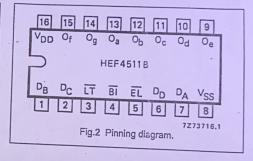

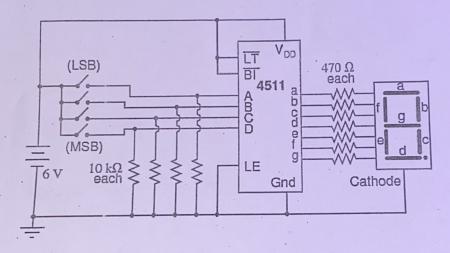

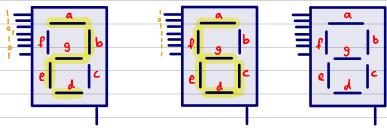

## BCD to 7-segment latch/decoder/driver

**HEF4511B** MSI

#### DESCRIPTION

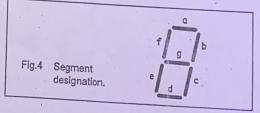

The HEF4511B is a BCD to 7-segment latch/decoder/driver with four address inputs (DA to DD), an active LOW latch enable input (EL), an active LOW ripple blanking input (BI), an active LOW lamp test input (LT), and seven active HIGH n-p-n bipolar transistor segment outputs (Oa to Og).

6 DR DD LATCHES DECODER LT DRIVERS 0d 0c 10 11 7273717.2 Fig.1 Functional diagram.

When EL is LOW, the state of the segment outputs (Oa to Og) is determined by the data on DA to DD. When EL goes HIGH, the last data present on DA to D<sub>D</sub> are stored in the latches and the segment outputs remain stable. When LT is LOW, all the segment outputs are HIGH independent of all other input conditions. With LT HIGH, a LOW on BI forces all segment outputs LOW. The inputs LT and BI do not affect the latch circuit.

HEF4511BP(N): 16-lead DIL; plastic (SOT38-1)

HEF4511BD(F): 16-lead DIL; ceramic (cerdip) (SOT74) HEF4511BT(D):

16-lead SO; plastic (SOT109-1)

(): Package Designator North America

### PINNING

DA to DD address (data) inputs EL latch enable input (active LOW) BI ripple blanking input (active LOW) LT lamp test input (active LOW) Oa to Og segment outputs

FAMILY DATA, IDD LIMITS category MSI See Family Specifications

Design a circuit and write a code for a stopwatch timer. The maximum time that it is count 60s. The result should be display on a seven segment

#### SCHEMATIC DIAGRAM

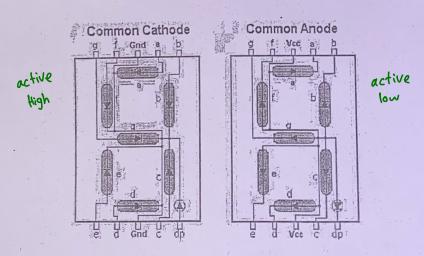

Figure 9 – Common Cathode & Common Anode

How can we get this using code?

We need to count the number of

$$10s$$

W=  $45$

$35$

$x = 1$

$10$

$35$

$x = 2$

$10$

$25$

After swap:

$x = 4$

$10 = 10$

$x = 4$

$x$

L1 Subwf

$$BCD1,1$$

;  $BCD1 = BCD1 - W$

BN L2; will check if negative bit is 1, if it is

|             | Communication to | Common cutto do                  |

|-------------|------------------|----------------------------------|

| <br>Digit   | abcdefg          | <u>common cathode</u><br>abcdefg |

| 0           |                  | 111110                           |

|             | 000000           |                                  |

|             | 1001111          | 0110000                          |

| 2           | 00   00   0      | 1101101                          |

| 3           | 0000110          | 1111001                          |

| 4           | 1001100          | 0110011                          |

| 5           | 0100100          | 1011011                          |

| 6           | 0100000          | 101111                           |

| 7           | 0001111          | 1110000                          |

| 8           | 000000           |                                  |

| 9           | 0000100          | 111 (01)                         |

|             | 1                | 7                                |

|             | we need to       | we need to                       |

|             | supply VCC and   | supply ground and                |

|             | (Low) to turn    | (High) to turn                   |

|             | on the segment   |                                  |

|             | on the styliner. |                                  |

|             |                  | Common Cathodi                   |

|             |                  |                                  |

| a, '        |                  |                                  |

| <u>'</u> '' | <b>3</b> f a b   |                                  |

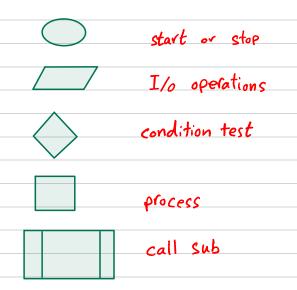

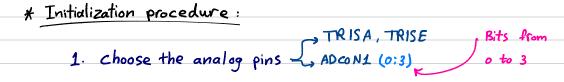

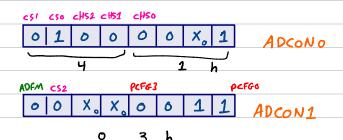

## Flow charts

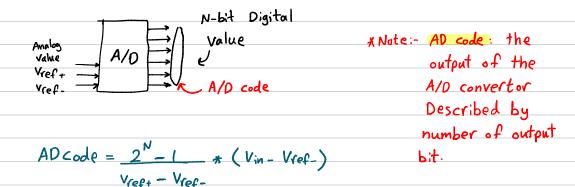

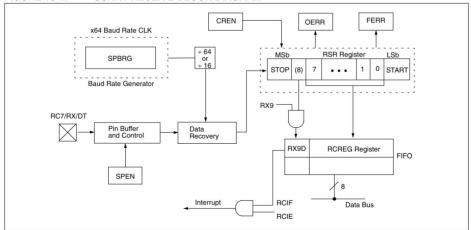

In PICI8FXX2 microprocessor, there is a built-in analog to digital module to convert an analog input signal (ex: voltage) to a 10-bit digital number.

\* computers can only understand digital signals.

-> Resolution: number of discrete values produced over the range of analog values.

[Vref., Vref.]

$$\Rightarrow$$

The range of analog value that the A/D Low 3 high 3 convertor can detect

Voltage resolution = The smallest change in voltage an ADC can detect

\* our ADC has a 10-bit resolution so N= 10.

\* The result of conversion is stored in SFRS, ADRESH

\* SFRs used 8-

TRISA, TRISE J for initialization ADCONO, ADCON1

ADREST 3 store the Result (stores the ADCODE)

# we need to define port A and port E as input or output and as Analog or digital.

operation of

the A/D module

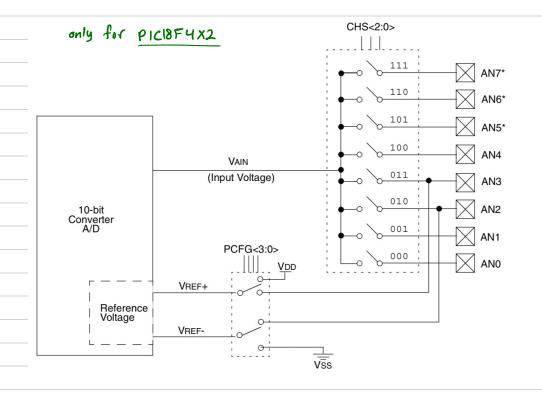

#### 17.0 COMPATIBLE 10-BIT SFRS ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) converter module has five inputs for the PIC18F2X2 devices and eight for the PIC18F4X2 devices. This module has the ADCON0 and ADCON1 register definitions that are compatible with the mid-range A/D module.

The A/D allows conversion of an analog input signal to a corresponding 10-bit digital number.

The A/D module has four registers. These registers controlles the

A/D Result High Register (ADRESH)

A/D Result Low Register (ADRESL) A/D Control Register 0 (ADCON0)

A/D Control Register 1 (ADCON1) \*

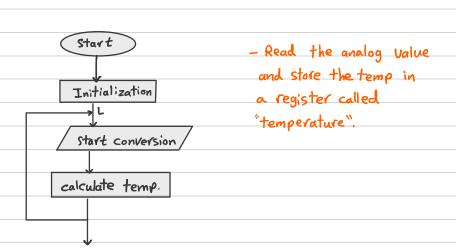

The ADCON0 register, shown in Register 17-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 17-2, configures the \* functions of the port pins.

bit recolution

REGISTER 17-1: ADCONO REGISTER

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | U-0 | R/W-0 |

|-------|-------|-------|-------|-------|---------|-----|-------|

| ADCS1 | ADCS0 | CHS2  | CHS1  | CHS0  | GO/DONE | _   | ADON  |

| bit 7 |       |       |       |       |         | 1   | bit 0 |

bit 7-6 ADCS1:ADCS0: A/D Conversion Clock Select bits (ADCON0 bits in bold)

| ADCON1<br><adcs2></adcs2>             | ADCON0<br><adcs1:adcs0></adcs1:adcs0> | Clock Conversion                                        |  |        |  |

|---------------------------------------|---------------------------------------|---------------------------------------------------------|--|--------|--|

| 0                                     | 00                                    | Fosc/2                                                  |  | $\neg$ |  |

| 0                                     | 01                                    | Fosc/8                                                  |  | П.     |  |

| 0                                     | 10                                    | Fosc/32                                                 |  | $\neg$ |  |

| 0                                     | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |  |        |  |

| 1                                     | 0.0                                   | Fosc/4                                                  |  |        |  |

| 1                                     | 01                                    | Fosc/16                                                 |  |        |  |

| 1                                     | 10                                    | Fosc/64                                                 |  |        |  |

| 1                                     | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |  | П      |  |

| CHS2:CHS0: Analog Channel Select bits |                                       |                                                         |  |        |  |

bit 5-3 CHS2:CHS0: Analog Channel Select bits

001 = channel 1, (AN1)

010 = channel 2, (AN2)

011 = channel 3, (AN3)

000 = channel 0, (AN0) we choose and

based on it, we specify the channel 100 = channel 4, (AN4) 101 = channel 5, (AN5) 110 = channel 6, (AN6)

select bits. 111 = channel 7, (AN7)

Note: The PIC18F2X2 devices do not implement the full 8 A/D channels; the unimplemented selections are reserved. Do not select any unimplemented channel.

#### GO/DONE: A/D Conversion Status bit bit 2

When ADON = 1:

1 = A/D conversion in progress (setting this bit starts the A/D conversion which is automatically -> conversion from Analogue to Digital cleared by hardware when the A/D conversion is complete)

0 = A/D conversion not in progress

bit 1 Unimplemented: Read as '0'

bit 0 ADON: A/D On bit

1 = A/D converter module is powered up

0 = A/D converter module is shut-off and consumes no operating current

Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

PCFG (0-3)

REGISTER 17-2: ADCON1 REGISTER

| R/W-0 | R/W-0 | U-0 | U-0  | R/W-0 | R/W-0   | R/W-0  | R/W-0 |

|-------|-------|-----|------|-------|---------|--------|-------|

| ADFM  | ADCS2 | - X | - X  | PCFG3 | PCFG2   | PCFG1  | PCFG0 |

| bit 7 |       |     | L De | not c | are, ju | st put | bit 0 |

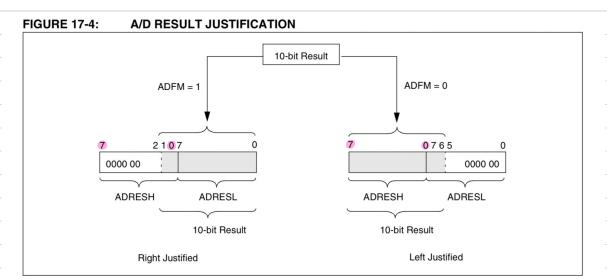

bit 7 ADFM: A/D Result Format Select bit

1 = Right justified. Six (6) Most Significant bits of ADRESH are read as '0'.

0 = Left justified. Six (6) Least Significant bits of ADRESL are read as '0'.

ADCS2: A/D Conversion Clock Select bit (ADCON1 bits in bold) bit 6

Table 1

| ADCON1<br><adcs2></adcs2> | ADCON0<br><adcs1:adcs0></adcs1:adcs0> | Clock Conversion                                        |

|---------------------------|---------------------------------------|---------------------------------------------------------|

| 0                         | 0.0                                   | Fosc/2                                                  |

| 0                         | 01                                    | Fosc/8                                                  |

| 0                         | 10                                    | Fosc/32                                                 |

| 0                         | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |

| 1                         | 0.0                                   | Fosc/4                                                  |

| 1                         | 01                                    | Fosc/16                                                 |

| 1                         | 10                                    | Fosc/64                                                 |

| 1                         | 11                                    | FRC (clock derived from the internal A/D RC oscillator) |

bit 5-4 Unimplemented: Read as '0'

PCFG3:PCFG0: A/D Port Configuration Control bits bit 3-0

if there is no VREF-

or VREF+ , it means it's internal

external VREF+ =

| PCFG<br><3:0> | AN7 | AN6 | AN5 | AN4 | AN3   | AN2   | AN1 | AN0 | VREF+ | VREF- | C/R   |

|---------------|-----|-----|-----|-----|-------|-------|-----|-----|-------|-------|-------|

| 0000          | Α   | Α   | Α   | Α   | Α     | Α     | Α   | Α   | VDD   | Vss   | 8/0   |

| 0001          | Α   | Α   | Α   | Α   | VREF+ | Α     | Α   | Α   | AN3   | Vss   | 7/1   |

| 0010          | D   | D   | D   | Α   | Α     | Α     | Α   | Α   | VDD   | Vss   | 5/0   |

| 0011          | D   | D   | D   | Α   | VREF+ | Α     | Α   | Α   | AN3   | Vss   | 4/1   |

| 0100          | D   | D   | D   | D   | Α     | D     | Α   | Α   | VDD   | Vss   | 3/0   |

| 0101          | D   | D   | D   | D   | VREF+ | D     | Α   | Α   | AN3   | Vss   | 2/1   |

| 011x          | D   | D   | D   | D   | D     | D     | D   | D   | _     | _     | 0/0   |

| 1000          | Α   | Α   | Α   | Α   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 6/2   |

| 1001          | D   | D   | Α   | Α   | Α     | Α     | Α   | Α   | VDD   | Vss   | 6/0   |

| 1010          | D   | D   | Α   | Α   | VREF+ | Α     | Α   | Α   | AN3   | Vss   | 5 / 1 |

| 1011          | D   | D   | Α   | Α   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 4/2   |

| 1100          | D   | D   | D   | Α   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 3/2   |

| 1101          | D   | D   | D   | D   | VREF+ | VREF- | Α   | Α   | AN3   | AN2   | 2/2   |

| 1110          | D   | D   | D   | D   | D     | D     | D   | Α   | VDD   | Vss   | 1/0   |

| 1111          | D   | D   | D   | D   | VREF+ | VREF- | D   | Α   | AN3   | AN2   | 1/2   |

|               |     |     |     |     |       |       |     |     |       |       | 1-0   |

A = Analog input D = Digital I/O

C/R = # of analog input channels / # of A/D voltage references

Table 2

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

On any device RESET, the port pins that are multiplexed with analog functions (ANx) are Note: forced to be an analog input.

- 2. choose Vief internal or external -> ADCON1 (0:3)

- 3. Choose A/D conversion clock -> ADCONO (7,6)

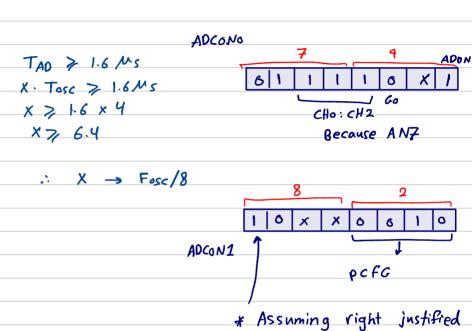

## Example: Fose = 4 MHz

\* out of the options in Table 1, we can choose x to be 8, 16, 32, 64 which any of them works but the best thing is to choose the smallest.

we take ADCSO, ADCS1 and ADCS2 bits that corresponds to Fosc/8 and put them in bits 6 and 7 of ADCON1

Q: in the A/D module for 18F452 what is the maximum frequency for the conversion clock

(Fost = 4MHz)

A/D Example: a temperature sensor LM35 is used to measure the Room

temp. the sensor gain is 10 mV/c° and the temp. range

is from (o-100°c)

Sensor Voltage range =

temp range x sensor gain

Input is temp

output is Voltage

Which is the

input to the

microcontroller.

Initialization procedure:

1) we need to determine viet, do we want internal or external.

Internal Vief >> Voltage resolution = 5/1024 = 0.0048 V /ADCODE

⇒ : temp resolution → 4.8 mv/ADCODE

= 0.48 C°/ADCODE

External voltage => (we need to choose the value)

: Voltage resolution = 1/1024 = 0.00097 V/ADCODE

= 0.97 mv/ADCODE : temp (esolution = 0.097 c°/ADcode

\* So we will choose the External Voltage since it gives higher precision

2 calculate conversion clock where fose = 4MHZ

TAD > 1.6 MS X. Telk > 1.6 MS

$X \cdot \frac{1}{y} Ms \geqslant 1.6 Ms$   $X \geqslant 6.4$   $\therefore X = 8$

from the ADCS 2 ADCS 1 ADCSO Fose, Data sheet 0 0 1

3 choose the analog pin that will be used ⇒ we will choose analog pin ANO

\* in this case, we could've used AN2 since we don't want an external Vref - BUT, since we want an external Vref + then we can't use AN3.

⇒ now we need to choose a pcFG (from Table 2) that has an analog pin at ANO and an external Vref + at AN3. Available options: 0001

0011/ I can choose

0101 any.

1010

## 4 ADFM

-> we want to store the conversion output using Left justification, so ADFM = 0

\* cHS2: CHSO are analog channel select bit, which we get based on the analog pin we chose.

$$ANO \rightarrow channel O = OOO$$

- calculate the relation between ADCODE and the room temperature

> Let's say that the temp is look which means that  $V_{in} = 1 \text{ Volt} \Rightarrow ADCODE = (||||||||||)_2 = (1023)_{10}$ but how will we read the temp from the ADCODE? we need a way that converts ADCODE to temp.

The input Voltage to Vin = sensor gain + Room temp the pic which is the Vin = 10 x 103 + T output voltage of the temp sensor.

$$ADCODE = \frac{2^{10} - 1}{1 - 0} * Vin = 1023 * 10 * 10^{-3} * T$$

$$Vref * - Vref - T = \frac{ADCODE}{1023 * 10 * 10^{-3}} = \frac{ADCODE}{10.23} * \frac{ADCODE}{10}$$

+ Note: In the instruction set there is No divesion so will use RR (Rotate Right) => shift Right x by one bit = X/2

now we need to find a way to do ADCODE/10

RR 3 time 5 times 6 times

$$\frac{X}{10} = \frac{X}{8} = \frac{X}{32}$$

0.125 X 0.03125 X 0.015625 X = 0.109 X

This is close to 0.1 X that we're looking for but we can be more accurate.

```

Main:

; Initialization

Value 1 = ADCODE/8

bsf TRISA, o

MOVIW 0X41

Value 2 = ADCODE/32

Value 3 = ADCODE/64

MOVWE ADCONO

MOV LW OXO?

> pin 0 of port A is set to

MOVWF ADCON1

be an input.

L, bsf ADCONO, 2

L2 btfsc ADCONO, 2

goto L2

MoVfl ADRESH, Value 1 ⇒ ADCODE/4

RRNC Value 1, F 7 Both of these will

bef Value 1, 7 I do a shift right => ADCODE/8

Mouff Value 1, Value 2

RRNC Value 2, 1 1

bcf value 2, 7 ) ⇒ AD CODE/16

RRNC Value 2, 17

bcf Value2, 7 S → ADCODE/32

Movff Value2, Value3

RRNC value 3, 1 7

bcf value 3, 7 S ⇒ ADCODE/64

Movf Value2, w

Value2

Subwf Value1, w - w = Value1 - w

ADDWF Value3, w -> w = Value3 + w = Value3 + Value1 - Value2

Movuf Temperature > 2 ADCODE/10

```

## Some code explanations-

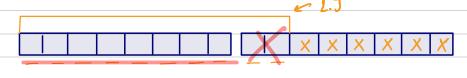

1 Movff ADRESH, Value 1 ⇒ ADCODE/4

when initializing, we chose Left justification which would look like:

ADRESH

ADRESL

usally when we do a shift Right (for division)

we lose that first bit.

when we took only the contents of ADRESH, it's

like we lost the 2 first bits (shift right twice)

which means divided by 2 twice : ADCODE/4.

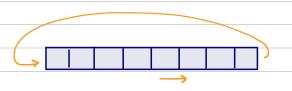

2 RRNC Value 1, F 3 bcf Value 1, 7 3 ⇒ ADCODE/8

in the instruction set, there is no shift right, but there is a rotate right.

to the right, but

the first bit goes to

the last bit so we

need to clear that last

bit to do a real shift.

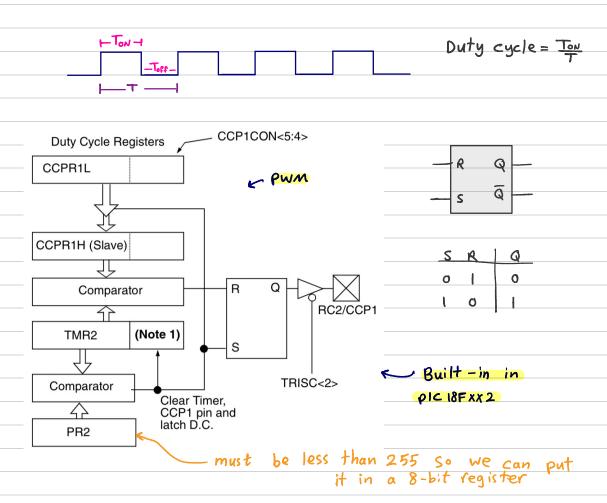

# pulse width modulation (pwn)

SFR's:

$\frac{\cancel{\times}}{\cancel{\times}} < 3: 0 > \rightarrow \text{ bits}$

TRISC,2

RC2 -> The only pin that can output the pwm's waveform.

prescale value <1:0>

T2CON \_\_\_\_, TMR2ON <27

CCPICON & pwm module < 3:0>

CCPRIL -> MSB's of Duty cycle

pr2 \_\_\_\_\_\_ A period register in the timer module.

Town = [PR2+1] \* 4 \* Tose \* prescale

Ton = [x] \* Tosc \* prescale

X > [ccpR1L: ccp1coN < 5:4>] a 10 bit number.

Example: fosc = 1 MHz Tpum = 30 Ms Duty cycle = 50%

30 NS = [PR2+1] \* 4 \* 1 NS \* prescale

7.5 = [PR2+1] \* Prescale

\* we choose the prescale

PR2 = 6.5

Value 5 1:1

> if > 255 we should think of a prescale value that is larger than 1.

L1:16

1:4

we don't have 0.5 so either PR2=7 or 6

in pre being an integer.

Main:

$$X = 150 = 201001010$$

T2CON

Xº 0 0 0 0 1 0 1

Mains

CCP1CON X X

bef LATE, 2

bef TRISE, 2

MOVEN OXYA

MOVEN PR2

MOVIN OX2C

MOVEN CCPICON

MOVIN OX25

MOVEN OX25

MOVEN OX05

MOVEN OX05

MOVEN OX05

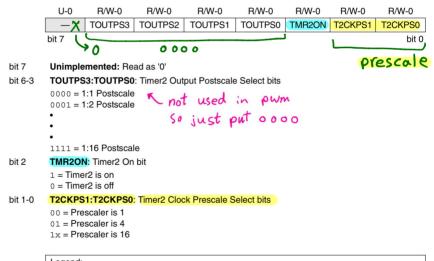

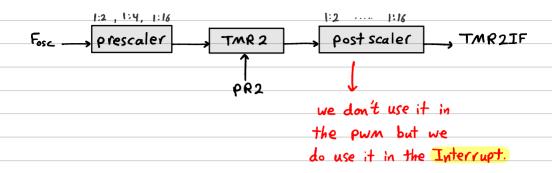

#### 12.0 TIMER2 MODULE

The Timer2 module timer has the following features:

- 8-bit timer (TMR2 register)

- 8-bit period register (PR2)

- · Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

- · Interrupt on TMR2 match of PR2

- SSP module optional use of TMR2 output to generate clock shift

Timer2 has a control register shown in Register 12-1. Timer2 can be shut-off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption. Figure 12-1 is a simplified block diagram of the Timer2 module. Register 12-1 shows the Timer2 control register. The prescaler and postscaler selection of Timer2 are controlled by this register.

#### 12.1 Timer2 Operation

Timer2 can be used as the PWM time-base for the PWM mode of the CCP module. The TMR2 register is readable and writable, and is cleared on any device RESET. The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>). The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

The prescaler and postscaler counters are cleared when any of the following occurs:

- · a write to the TMR2 register

- · a write to the T2CON register

- any device RESET (Power-on Reset, MCLR Reset, Watchdog Timer Reset, or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

#### REGISTER 12-1: T2CON: TIMER2 CONTROL REGISTER

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### 14.0 CAPTURE/COMPARE/PWM (CCP) MODULES

Each CCP (Capture/Compare/PWM) module contains a 16-bit register which can operate as a 16-bit Capture register, as a 16-bit Compare register or as a PWM Master/Slave Duty Cycle register. Table 14-1 shows the timer resources of the CCP Module modes.

The operation of CCP1 is identical to that of CCP2, with the exception of the special event trigger. Therefore, operation of a CCP module in the following sections is described with respect to CCP1.

Table 14-2 shows the interaction of the CCP modules.

#### REGISTER 14-1: CCP1CON REGISTER/CCP2CON REGISTER

| U-0                        | U-0        | R/W-0 | R/W-0 | R/W-0      | R/W-0  | R/W-0  | R/W-0  |  |  |

|----------------------------|------------|-------|-------|------------|--------|--------|--------|--|--|

| - ×                        | — <b>X</b> | DCxB1 | DCxB0 | CCPxM3     | CCPxM2 | CCPxM1 | CCPxM0 |  |  |

| bit 7 👩                    | 0          |       |       |            |        |        | bit 0  |  |  |

|                            |            |       | C     | - The      | LSBs   | of ti  | 18     |  |  |

| Unimplemented: Read as '0' |            |       |       | Duty cycle |        |        |        |  |  |

bit 7-6 Unimplemented: Read as '0'

bit 5-4 DCxB1:DCxB0: PWM Duty Cycle bit1 and bit0

Capture mode:

Unused

Compare mode:

Unused

PWM mode:

These bits are the two LSbs (bit1 and bit0) of the 10-bit PWM duty cycle. The upper eight bits

(DCx9:DCx2) of the duty cycle are found in CCPRxL.

bit 3-0 CCPxM3:CCPxM0: CCPx Mode Select bits

0000 = Capture/Compare/PWM disabled (resets CCPx module)

0001 = Reserved

0010 = Compare mode, toggle output on match (CCPxIF bit is set)

0011 = Reserved

0100 = Capture mode, every falling edge

0101 = Capture mode, every rising edge

0110 = Capture mode, every 4th rising edge

0111 = Capture mode, every 16th rising edge 1000 = Compare mode,

Initialize CCP pin Low, on compare match force CCP pin High (CCPIF bit is set)

1001 = Compare mode.

Initialize CCP pin High, on compare match force CCP pin Low (CCPIF bit is set)

1010 = Compare mode.

Generate software interrupt on compare match (CCPIF bit is set, CCP pin is unaffected)

1011 = Compare mode,

Trigger special event (CCPIF bit is set)

11xx = PWM mode

| Legend:            |                  |                                    |                    |  |

|--------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

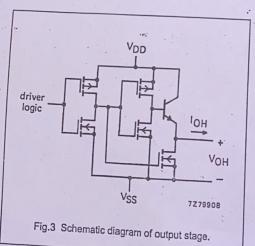

#### 14.5 PWM Mode

In Pulse Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

Note: Clearing the CCP1CON register will force the CCP1 PWM output latch to the default low level. This is not the PORTC I/O data latch.

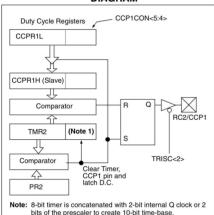

Figure 14-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see Section 14.5.3.

# FIGURE 14-3: SIMPLIFIED PWM BLOCK DIAGRAM

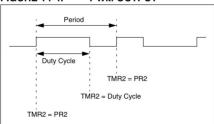

A PWM output (Figure 14-4) has a time-base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

FIGURE 14-4: PWM OUTPUT

#### 14.5.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- · TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

Note: The Timer2 postscaler (see Section 12.0) is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

#### 14.5.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2 concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by the equation:

$$PWM ext{ Resolution (max)} = \frac{\log\left(\frac{FOSC}{FPWM}\right)}{\log(2)} bits$$

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

# Interrupts

-> an interrupt is a sub routine (function) that gets called automatically when a certain condition is met and when it's done, the code resumes from the line it was last on in the main code.

(it will interrupt the main code when a condition is met)

Interrupt name:

retfie

SFRs used:

RCON

INTCON

INTCON2

INTCON3

PIR1, PIR2

PIE1, PIE2

IPR1, IPR2

Internal - Timer, ccp, A/D,

Serial communication ....

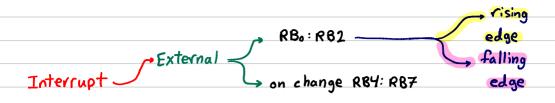

The signal/condition that will trigger the interrupt to be called can be external or internal

in external interrupt, each bit is independent from bits o to 3. Whereas the onchange takes 4 bits (4:7) as one data, so if it was oolo and became oooo it will trigger the interrupt for example.

for example port B < 4:7>

0110 0000

<4:7>

becomes 0010 0000 changed -> so there is an interrupt

\* If there is at least one bit that changes from bits <4:7>

an interrupt will occur.

# For each interrupt has:

- 1. Enable bit TF

- IF Automatically set, manually reset 2. Flag bit 3. priority bit Ip

- \* The enable bit is to tell the microcontroller which interrupt registors we want to use

- \* if a certain condition is met, the microcontroller automatically sets the flag bit and we have to manually reset it (clear) before we return from the interrupt because if we didn't and we returned from the interrupt, the microcontroller will see that the flag bit is still set so it will enter the interrupt again.

- > To enable the priority feature: IPEN bit (RCON<7>) in general

- 1: 2 levels of priority Default - 0: 1 level of priority

rising edge 1

falling edge

# INTEDG 0, 1, 2 in INTCON2 Edge bits for port 80: 82 0 -> falling 1 -> rising Hardware decides the falling or rising case 1: IPEN (set)

- GIEH bit (INTCON<7>) enable all Int. high priority

GIEL bit (INTCON<6>) // // // LOW //

- case 2: IPEN (clear)

- GIE bit (INTCON<7>) enable all interrupt source - PFIE bit (INTCON<6>) enable peripherals interrupt

- \* NoTE ? There is no bit for priority selection of external INTO. Its always at high interrupt level and can't be changed to low

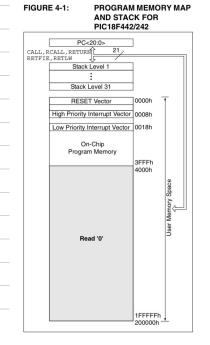

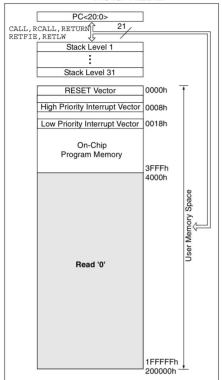

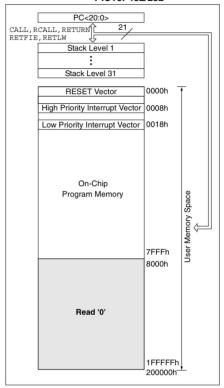

FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR PIC18F442/242

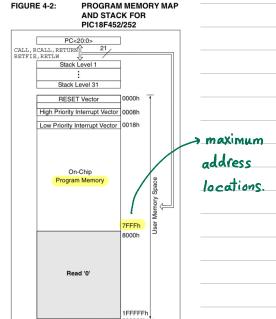

FIGURE 4-2: PROGRAM MEMORY MAP AND STACK FOR PIC18F452/252

#### 8.0 INTERRUPTS

The PIC18FXX2 devices have multiple interrupt sources and an interrupt priority feature that allows each interrupt source to be assigned a high priority level or a low priority level. The high priority interrupt vector is at 000008h and the low priority interrupt vector is at 000018h. High priority interrupt events will override any low priority interrupts that may be in progress.

There are ten registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2

- PIE1, PIE2

- IPR1, IPR2

It is recommended that the Microchip header files supplied with MPLAB® IDE be used for the symbolic bit names in these registers. This allows the assembler/compiler to automatically take care of the placement of these bits within the specified register.

Each interrupt source, except INT0, has three bits to control its operation. The functions of these bits are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- · Priority bit to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set. Setting the GIEL bit (INTCON-6>) enables all interrupts that have the priority bit cleared. When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 000008h or 000018h, depending on the priority level. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PICmicro® mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit, which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit, which enables/disables all interrupt sources. All interrupts branch to address 000008h in Compatibility mode.

When an interrupt is responded to, the Global Interrupt Enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High priority interrupt sources can interrupt a low priority interrupt.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (000008h or 000018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INT pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding enable bit or the GIE bit.

Note:

Do not use the MOVFF instruction to modify any of the Interrupt control registers while **any** interrupt is enabled. Doing so may cause erratic microcontroller behavior.

#### 8.1 **INTCON Registers**

The INTCON Registers are readable and writable registers, which contain various enable, priority and flag bits.

Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

#### REGISTER 8-1: INTCON REGISTER

| R/W-0    | R/W-0     | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-x |

|----------|-----------|--------|--------|-------|--------|--------|-------|

| GIE/GIEH | PEIE/GIEL | TMR0IE | INTOIE | RBIE  | TMR0IF | INT0IF | RBIF  |

| bit 7    |           |        |        |       |        |        | bit 0 |

Note:

bit 7 GIE/GIEH: Global Interrupt Enable bit

#### When IPEN = 0:

- 1 = Enables all unmasked interrupts

- 0 = Disables all interrupts

#### When IPEN = 1:

- 1 = Enables all high priority interrupts

- 0 = Disables all interrupts

#### bit 6 PEIE/GIEL: Peripheral Interrupt Enable bit

#### When IPEN = 0:

- 1 = Enables all unmasked peripheral interrupts

- 0 = Disables all peripheral interrupts

#### When IPEN = 1:

- 1 = Enables all low priority peripheral interrupts

- 0 = Disables all low priority peripheral interrupts

#### bit 5 TMR0IE: TMR0 Overflow Interrupt Enable bit

- 1 = Enables the TMR0 overflow interrupt

- 0 = Disables the TMR0 overflow interrupt

- bit 4 INTOIE: INTO External Interrupt Enable bit

- 1 = Enables the INT0 external interrupt

- 0 = Disables the INT0 external interrupt

- bit 3 RBIE: RB Port Change Interrupt Enable bit

- 1 = Enables the RB port change interrupt 0 = Disables the RB port change interrupt

- bit 2

- TMR0IF: TMR0 Overflow Interrupt Flag bit 1 = TMR0 register has overflowed (must be cleared in software)

- 0 = TMR0 register did not overflow

- bit 1 INTOIF: INTO External Interrupt Flag bit

- 1 = The INT0 external interrupt occurred (must be cleared in software)

- 0 = The INT0 external interrupt did not occur

bit 0 RBIF: RB Port Change Interrupt Flag bit

Automatically 1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)

0 = None of the RB7:RB4 pins have changed state

Note: A mismatch condition will continue to set this bit. Reading PORTB will end the mismatch condition and allow the bit to be cleared.

Automatically set, manually

Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

flag bit initially

condition is met

o, if the

#### REGISTER 8-2: INTCON2 REGISTER

| R/W-1 | R/W-1   | R/W-1   | R/W-1   | U-0 | R/W-1  | U-0 | R/W-1 |  |

|-------|---------|---------|---------|-----|--------|-----|-------|--|

| RBPU  | INTEDG0 | INTEDG1 | INTEDG2 | _   | TMR0IP | _   | RBIP  |  |

| bit 7 |         |         |         |     |        |     | bit 0 |  |

bit 7 RBPU: PORTB Pull-up Enable bit

1 = All PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual port latch values

bit 6 INTEDG0:External Interrupt0 Edge Select bit

1 = Interrupt on rising edge

0 = Interrupt on falling edge

bit 5 INTEDG1: External Interrupt1 Edge Select bit

1 = Interrupt on rising edge

0 = Interrupt on falling edge

bit 4 INTEDG2: External Interrupt2 Edge Select bit

1 = Interrupt on rising edge

0 = Interrupt on falling edge

bit 3 Unimplemented: Read as '0'

bit 2 TMR0IP: TMR0 Overflow Interrupt Priority bit

1 = High priority

0 = Low priority

bit 1 Unimplemented: Read as '0'

bit 0 RBIP: RB Port Change Interrupt Priority bit

1 = High priority

0 = Low priority

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

#### REGISTER 8-3: INTCON3 REGISTER

| R/W-1  | R/W-1  | U-0 | R/W-0  | R/W-0  | U-0 | R/W-0  | R/W-0  |

|--------|--------|-----|--------|--------|-----|--------|--------|

| INT2IP | INT1IP | _   | INT2IE | INT1IE | _   | INT2IF | INT1IF |

| bit 7  |        |     |        |        |     |        | bit 0  |

bit 7 INT2IP: INT2 External Interrupt Priority bit

1 = High priority 0 = Low priority

bit 6 INT1IP: INT1 External Interrupt Priority bit

1 = High priority

0 = Low priority

bit 5 Unimplemented: Read as '0'

bit 4 INT2IE: INT2 External Interrupt Enable bit

1 = Enables the INT2 external interrupt

0 =Disables the INT2 external interrupt

bit 3 INT1IE: INT1 External Interrupt Enable bit

1 = Enables the INT1 external interrupt0 = Disables the INT1 external interrupt

0 = Disables the INTT external litter

bit 2 Unimplemented: Read as '0'

bit 1 INT2IF: INT2 External Interrupt Flag bit

1 = The INT2 external interrupt occurred (must be cleared in software)

0 = The INT2 external interrupt did not occur

bit 0 INT1IF: INT1 External Interrupt Flag bit

1 = The INT1 external interrupt occurred (must be cleared in software)

0 = The INT1 external interrupt did not occur

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

#### 8.2 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Flag Registers (PIR1, PIR2).

- Note 1: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit. GIE (INTCON<7>).

- User software should ensure the appropriate interrupt flag bits are cleared prior to enabling an interrupt, and after servicing that interrupt.

#### REGISTER 8-4: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1

| R/W-0                | R/W-0 | R-0  | R-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  |  |

|----------------------|-------|------|------|-------|--------|--------|--------|--|

| PSPIF <sup>(1)</sup> | ADIF  | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF |  |

| bit 7                |       |      |      |       |        |        | bit 0  |  |

- bit 7 PSPIF<sup>(1)</sup>: Parallel Slave Port Read/Write Interrupt Flag bit

- 1 = A read or a write operation has taken place (must be cleared in software)

- 0 = No read or write has occurred

- bit 6 ADIF: A/D Converter Interrupt Flag bit

- 1 = An A/D conversion completed (must be cleared in software)

- 0 = The A/D conversion is not complete

- bit 5 RCIF: USART Receive Interrupt Flag bit

- 1 = The USART receive buffer, RCREG, is full (cleared when RCREG is read)

- 0 = The USART receive buffer is empty

- bit 4 TXIF: USART Transmit Interrupt Flag bit (see Section 16.0 for details on TXIF functionality)

- 1 = The USART transmit buffer, TXREG, is empty (cleared when TXREG is written)

- 0 = The USART transmit buffer is full

- bit 3 SSPIF: Master Synchronous Serial Port Interrupt Flag bit

- 1 = The transmission/reception is complete (must be cleared in software)

- 0 = Waiting to transmit/receive

- bit 2 CCP1IF: CCP1 Interrupt Flag bit

#### Capture mode:

- 1 = A TMR1 register capture occurred (must be cleared in software)

- 0 = No TMR1 register capture occurred

#### Compare mode:

- 1 = A TMR1 register compare match occurred (must be cleared in software)

- 0 = No TMR1 register compare match occurred

#### PWM mode:

Unused in this mode

- bit 1 TMR2IF: TMR2 to PR2 Match Interrupt Flag bit

- 1 = TMR2 to PR2 match occurred (must be cleared in software)

- 0 = No TMR2 to PR2 match occurred

- bit 0 TMR1IF: TMR1 Overflow Interrupt Flag bit

- 1 = TMR1 register overflowed (must be cleared in software)

- 0 = MR1 register did not overflow

Note 1: This bit is reserved on PIC18F2X2 devices; always maintain this bit clear.

| Legend:                           |                  |                                    |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

| - n = Value at POR                | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### REGISTER 8-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  |  |

|-------|-----|-----|-------|-------|-------|--------|--------|--|

| _     | _   | _   | EEIF  | BCLIF | LVDIF | TMR3IF | CCP2IF |  |

| bit 7 |     |     |       |       |       |        | bit 0  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4

EEIF: Data EEPROM/FLASH Write Operation Interrupt Flag bit

1 = The Write operation is complete (must be cleared in software)

0 = The Write operation is not complete, or has not been started

bit 3 BCLIF: Bus Collision Interrupt Flag bit

1 = A bus collision occurred (must be cleared in software)

0 = No bus collision occurred

bit 2 LVDIF: Low Voltage Detect Interrupt Flag bit

1 = A low voltage condition occurred (must be cleared in software) 0 = The device voltage is above the Low Voltage Detect trip point

bit 1 TMR3IF: TMR3 Overflow Interrupt Flag bit

1 = TMR3 register overflowed (must be cleared in software)

0 = TMR3 register did not overflow

bit 0 CCP2IF: CCPx Interrupt Flag bit

Capture mode:

1 = A TMR1 register capture occurred (must be cleared in software)

0 = No TMR1 register capture occurred

Compare mode:

1 = A TMR1 register compare match occurred (must be cleared in software)

0 = No TMR1 register compare match occurred

PWM mode:

Unused in this mode

Legend:

R = Readable bit  $W = Writable \ bit$   $U = Unimplemented \ bit, read as '0' - n = Value \ at POR$  '1' = Bit is set '0' = Bit is cleared  $x = Bit \ is \ unknown$

#### 8.3 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Enable Registers (PIE1, PIE2). When IPEN = 0, the PEIE bit must be set to enable any of these peripheral interrupts.

#### REGISTER 8-6: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|----------------------|-------|-------|-------|-------|--------|--------|--------|

| PSPIE <sup>(1)</sup> | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE |

| bit 7                | -     |       |       |       |        |        | bit 0  |

| bit 7  | PSPIE <sup>(1)</sup> : Parallel Slave Port Read/Write Interrupt Enable bit |

|--------|----------------------------------------------------------------------------|

|        | 1 = Enables the PSP read/write interrupt                                   |

|        | 0 = Disables the PSP read/write interrupt                                  |

| bit 6  | ADIE: A/D Converter Interrupt Enable bit                                   |

|        | 1 = Enables the A/D interrupt                                              |

|        | 0 = Disables the A/D interrupt                                             |

| 1.00 E | POIE HOADT Dead of the Live                                                |

bit 5 RCIE: USART Receive Interrupt Enable bit

1 = Enables the USART receive interrupt

0 = Disables the USART receive interrupt

bit 4 TXIE: USART Transmit Interrupt Enable bit

1 = Enables the USART transmit interrupt0 = Disables the USART transmit interrupt

bit 3 SSPIE: Master Synchronous Serial Port Interrupt Enable bit

1 = Enables the MSSP interrupt 0 = Disables the MSSP interrupt

bit 2 **CCP1IE**: CCP1 Interrupt Enable bit

1 = Enables the CCP1 interrupt

2 Picables the CCP1 interrupt

0 = Disables the CCP1 interrupt

bit 1 TMR2IE: TMR2 to PR2 Match Interrupt Enable bit

1 = Enables the TMR2 to PR2 match interrupt 0 = Disables the TMR2 to PR2 match interrupt

0 = Disables the TMR1 overflow interrupt

bit 0 TMR1IE: TMR1 Overflow Interrupt Enable bit

1 = Enables the TMR1 overflow interrupt

To compare the value of PR2 and TMR2

Note 1: This bit is reserved on PIC18F2X2 devices; always maintain this bit clear.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### REGISTER 8-7: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  |  |

|-------|-----|-----|-------|-------|-------|--------|--------|--|

| _     | _   | _   | EEIE  | BCLIE | LVDIE | TMR3IE | CCP2IE |  |

| bit 7 |     |     |       |       |       |        | hit 0  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4 **EEIE**: Data EEPROM/FLASH Write Operation Interrupt Enable bit

1 = Enabled 0 = Disabled

bit 3 BCLIE: Bus Collision Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 2 LVDIE: Low Voltage Detect Interrupt Enable bit

1 = Enabled 0 = Disabled

bit 1 TMR3IE: TMR3 Overflow Interrupt Enable bit

1 = Enables the TMR3 overflow interrupt

0 = Disables the TMR3 overflow interrupt

bit 0 CCP2IE: CCP2 Interrupt Enable bit

1 = Enables the CCP2 interrupt

0 = Disables the CCP2 interrupt

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### 8.4 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Priority Registers (IPR1, IPR2). The operation of the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

#### REGISTER 8-8: IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1

| R/W-1                | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1  | R/W-1  | R/W-1  |  |

|----------------------|-------|-------|-------|-------|--------|--------|--------|--|

| PSPIP <sup>(1)</sup> | ADIP  | RCIP  | TXIP  | SSPIP | CCP1IP | TMR2IP | TMR1IP |  |

| bit 7                |       |       |       |       |        |        | bit 0  |  |

bit 7 **PSPIP**<sup>(1)</sup>: Parallel Slave Port Read/Write Interrupt Priority bit

1 = High priority 0 = Low priority

bit 6 ADIP: A/D Converter Interrupt Priority bit

1 = High priority 0 = Low priority

bit 5 RCIP: USART Receive Interrupt Priority bit

1 = High priority

0 = Low priority

bit 4 TXIP: USART Transmit Interrupt Priority bit

1 = High priority 0 = Low priority

bit 3 SSPIP: Master Synchronous Serial Port Interrupt Priority bit

1 = High priority 0 = Low priority

bit 2 CCP1IP: CCP1 Interrupt Priority bit

1 = High priority 0 = Low priority

bit 1 TMR2IP: TMR2 to PR2 Match Interrupt Priority bit

1 = High priority

0 = Low priority

bit 0 TMR1IP: TMR1 Overflow Interrupt Priority bit

1 = High priority 0 = Low priority

Note 1: This bit is reserved on PIC18F2X2 devices; always maintain this bit set.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### REGISTER 8-9: IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1  | R/W-1  |

|-------|-----|-----|-------|-------|-------|--------|--------|

| _     | _   | _   | EEIP  | BCLIP | LVDIP | TMR3IP | CCP2IP |

| bit 7 |     |     |       |       |       |        | bit 0  |

bit 7-5 Unimplemented: Read as '0'

bit 4 **EEIP**: Data EEPROM/FLASH Write Operation Interrupt Priority bit

1 = High priority

0 = Low priority

bit 3 BCLIP: Bus Collision Interrupt Priority bit

1 = High priority

0 = Low priority

bit 2 LVDIP: Low Voltage Detect Interrupt Priority bit

1 = High priority 0 = Low priority

bit 1 TMR3IP: TMR3 Overflow Interrupt Priority bit

1 = High priority 0 = Low priority

bit 0 CCP2IP: CCP2 Interrupt Priority bit

1 = High priority

0 = Low priority

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### 8.5 RCON Register

The RCON register contains the bit which is used to enable prioritized interrupts (IPEN).

#### REGISTER 8-10: RCON REGISTER

we only need bit 7 bit 7

| R/W-0 | U-0 | U-0 | R/W-1 | R-1 | R-1 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-----|-----|-------|-------|

| IPEN  | _   | _   | RI    | TO  | PD  | POR   | BOR   |

| bit 7 |     |     |       |     |     |       | bit 0 |

IPEN: Interrupt Priority Enable bit

1 = Enable priority levels on interrupts

0 = Disable priority levels on interrupts (16CXXX Compatibility mode)

The mc will look for bit 6-5 Unimplemented: Read as '0' bit 4 RI: RESET Instruction Flag bit which interrupt has For details of bit operation, see Register 4-3 a High priority and bit 3 TO: Watchdog Time-out Flag bit which has a low one For details of bit operation, see Register 4-3 o : me will not look PD: Power-down Detection Flag bit bit 2 For details of bit operation, see Register 4-3 for priorities POR: Power-on Reset Status bit bit 1 and will generate interrupts at the some For details of bit operation, see Register 4-3 bit 0 **BOR:** Brown-out Reset Status bit For details of bit operation, see Register 4-3 time with no bias.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

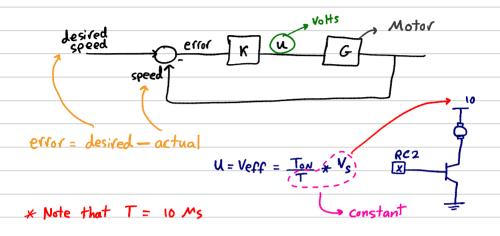

Example write Interrupt program to measure motor speed. optical encoder 1000 pulse/rev resolution Every 1ms the program will Active High find the speed Fosc = 4 MHz number of revolutions Pulse count resolution Motor speed = pulse count x 1 : Motor speed = pulse count - we want to count the number of pulses by counting each rising edge. -> Each time period we want to see how many pulses we counted. : we need 2 Interrupts to count rising edges > External; to count the pulses. RB1 (since an optical sensor is not inside the micro controller itself). . Internal; to access the timer TMR2

\* Note: If want to use the pwn as well as the Interrupt

first we need to find pR2 and initialize the

pwn and keep the prescale as is without adding the

post scale-yet. when we start initializing the Interrupt

we find the new PR2 by taking the same prescale and

adding the postscale.

$$|x|0^{-3} = [pR2 + 1] * |x|0^{-6} * prescale * postscale$$

$$[pR2 + 1] = |00|$$

$$\therefore pR2 = 99$$

$$prescale$$

$$|x|0 = |0|$$

Tritialization :-RSF INTCONS, INTITE; - Because we chose External PIE1, TMR2IE \* BSF and port B1 we had RCON, IPEN \* to look for the bit that BCF BSF enables the interrupt for INTCON2, INEDG1 that bit in the data sheet MOVLW 99 and found that it's in MOVWE PR2 MOVLW 0X48 INTCONS. T2CON MOVWE RSF INCON, PEIE \* we don't need priority so we clear that bit, it's BSF INCON, GIE BSF clear by default but just T2CON, 2 to make sure. return - we're assuming radix to be decimal which means if i put a number like 99 or \* Note that these file registers have named bits, so we can 48 the program will consider it access them using the bit number to be decimal so if we want

or the name of the bit.

To start the timer.

(TMR2)

\* To Activate timer and port B (enable).

Hexadecimal just put 0x48.

\* To Enable TMR2

### Int - Handler ?

INTCON3, INTLIF RTFSC pulse count goto count, speed; count = No. of pulses MOVFF CLRF count BCF PIR1, TMR2 IF goto

X

count. 1

pulse count BCF INTCON3, INTIIF

#### RETEIE LL

INCF

\* The optical encoder's output is pulses and we found a relation based on the resolution to find the speed, in this example it's the same as the pulse count.

\* There are 2 things that will cause an interrupt, external and the timer

\* we need to clear the flag bit of each interrupt, otherwise the micro controller will go back into the interrupt because it saw that the flag bit is set . (flag bit set = trigger an interrupt).

-> consider that pwn is already initialized

-> we will create a propotional controller to control the speed.

Ton = error Ms

```

Main:

CALL Initialization

MOVLW 100; The desired speed we want (decimal)

MOVWF desired - speed

MOVF speed, W

Subwf desired - speed, W; w = desired - speed - W

MOVWF CCPRIL

```

Note that e is error

# PID for Discrete Time

Note that K is sampling instant Note that To is Sampling time

Ts = Ims

GPR

$$\begin{cases} error i \Rightarrow e_1 + e_2 + e_3 + e_4 \dots + e_K \\ error \Rightarrow e_K \\ error d \Rightarrow e_{K-1} \end{cases}$$

errord = error - errorp

```

Main :

CALL Initialization

1. MOVLW 100; The desired speed we want (decimal)

MOVWF desired - speed

speed, w

MOVE

subwf desired-speed, w: w= desired-speed - w

MOVWF Prror

Addwf errori, 1

Movf errorp, w

subuf error, w; w = ex - ex-

Movuf errord

add wf error, w = ex + ex - ex-1

addwf errori, w \Rightarrow w = \rho + d + I

mover copril

MOVEE error p

goto L

```

# Serial communication

- 1. Synchronous > Information + clock

- 2. Asynchronous Just information

\* parallel and serial information

1. parallel: Information appear at once

EX CLRF TRISB DATA 01010101

MOVLW 0X08

MOVWF POTTB

B1 B5 B5

B4

\* We start from LSB to MSB

start -> 8 bit -> stop bit

DATA 1000 1000

Start Bo B1 B2 B4 B5 B6

2. series: Information Bit by Bit.

used SFRs:

TXSTA RCSTA SPBRG TXREG

used pins:

parity Bit:

even parity - o if No. of onest is even

\* The goal of the parity Bit is to make sure that

the Reciever recieved the information correctly

$$X = 10101000 \quad \text{parity Bit} = 1 \quad (odd)$$

# Band Rate Generator

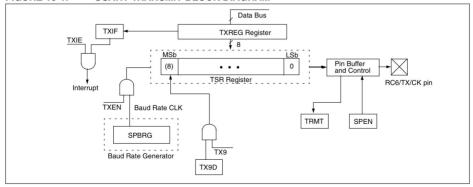

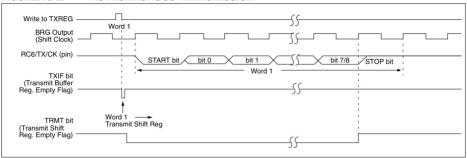

# 16.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI.) The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers, or it can be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The USART can be configured in the following modes:

- · Asynchronous (full-duplex)

- Synchronous Master (half-duplex)

- Synchronous Slave (half-duplex)

In order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter:

- bit SPEN (RCSTA<7>) must be set (= 1),

- bit TRISC<6> must be cleared (= 0), and

- bit TRISC<7> must be set (=1).

Register 16-1 shows the Transmit Status and Control Register (TXSTA) and Register 16-2 shows the Receive Status and Control Register (RCSTA).

| Transmitter | R/W-0                                       | R/W-0                                           | R/W-0         | R/W-0                | U-0                 | R/W-0      | R-1        | R/W-0    |

|-------------|---------------------------------------------|-------------------------------------------------|---------------|----------------------|---------------------|------------|------------|----------|

|             | CSRC                                        | TX9                                             | TXEN          | SYNC                 |                     | BRGH       | TRMT       | TX9D     |

|             | bit 7 X                                     |                                                 |               | 0                    | 0                   |            |            | bit 0    |

| bit 7       | CSRC: Clo                                   | ck Source Se                                    |               |                      |                     |            |            |          |

|             | Asynchron<br>Don't care                     | ous mode:                                       | → W<br>A      | e will a<br>synchron | nly use             |            |            |          |

|             |                                             | <u>us mode:</u><br>mode (clock<br>node (clock f |               |                      | n BRG)              |            |            |          |

| bit 6       | 1 = Selects                                 | Fransmit Ena<br>9-bit transm<br>8-bit transm    | ission        | → we                 | choose              | if we      | e wan      | t 4 or 8 |

| bit 5       | TXEN: Train<br>1 = Transm<br>0 = Transm     | E 1000 E 100 E                                  | bit           |                      |                     |            |            |          |

|             | Note:                                       | SREN/CREN                                       | l overrides T | XEN in SYN           | IC mode.            |            |            |          |

| bit 4       | 1 = Synchr                                  | ART Mode Sonous mode                            |               |                      |                     |            |            |          |

| bit 3       | Unimplem                                    | ented: Read                                     | as '0'        |                      |                     |            |            |          |

| bit 2       | BRGH: Hig                                   | h Baud Rate                                     | Select bit    |                      |                     |            |            |          |

|             | Asynchronous<br>1 = High sp<br>0 = Low sp   | peed                                            |               |                      |                     |            |            |          |

|             | Synchrono                                   |                                                 |               |                      |                     |            |            |          |

| bit 1       | Unused in TRMT: Train 1 = TSR er 0 = TSR fu | nsmit Shift Re                                  | egister Statu |                      |                     |            | \ <i>(</i> | a et ad  |

| bit 0       | <b>TX9D:</b> 9th                            | bit of Transm<br>dress/Data bi                  |               | oit.                 | f 9 Bit<br>his is a | where h    | re put     | the      |

|             | Legend:                                     |                                                 |               |                      |                     |            |            |          |

|             | 1                                           | ble bit                                         |               | itable bit           |                     | lemented b |            |          |

'1' = Bit is set

'0' = Bit is cleared

- n = Value at POR

x = Bit is unknown

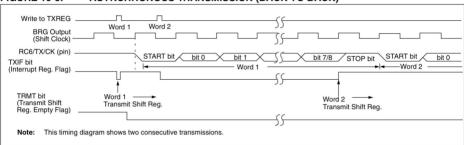

#### **REGISTER 16-2:** RCSTA: RECEIVE STATUS AND CONTROL REGISTER

Receiver R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R-0 R-0 R-x SPEN RX9 SREN **CREN** ADDEN **FERR OERR** RX9D bit 7

bit 0

bit 7 SPEN: Serial Port Enable bit

1 = Serial port enabled (configures RX/DT and TX/CK pins as serial port pins)

0 = Serial port disabled

bit 6 RX9: 9-bit Receive Enable bit

1 = Selects 9-bit reception

0 = Selects 8-bit reception

bit 5 SREN: Single Receive Enable bit

Asynchronous mode:

Don't care

Synchronous mode - Master:

1 = Enables single receive

0 = Disables single receive

This bit is cleared after reception is complete.

Synchronous mode - Slave:

Don't care

bit 4 CREN: Continuous Receive Enable bit

Asynchronous mode:

1 = Enables receiver

0 = Disables receiver

Synchronous mode:

1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)

0 = Disables continuous receive

bit 3 ADDEN: Address Detect Enable bit

Asynchronous mode 9-bit (RX9 = 1):

1 = Enables address detection, enable interrupt and load of the receive buffer

when RSR<8> is set

0 = Disables address detection, all bytes are received, and ninth bit can be used as parity bit

bit 2 FERR: Framing Error bit

1 = Framing error (can be updated by reading RCREG register and receive next valid byte)

0 = No framing error

bit 1 **OERR**: Overrun Error bit

1 = Overrun error (can be cleared by clearing bit CREN)

0 = No overrun error

bit 0 RX9D: 9th bit of Received Data

This can be Address/Data bit or a parity bit, and must be calculated by user firmware.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 16.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 16-1 shows the formula for computation of the baud rate for different USART modes, which only apply in Master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 16-1. From this, the error in baud rate can be determined.

Example 16-1 shows the calculation of the baud rate error for the following conditions:

- Fosc = 16 MHz

- · Desired Baud Rate = 9600

- BRGH = 0

- SYNC = 0

It may be advantageous to use the high baud rate (BRGH = 1) even for slower baud clocks. This is because the Fosc/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### 16.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

#### EXAMPLE 16-1: CALCULATING BAUD RATE ERROR

| Desired Baud Rate    | = $Fosc / (64 (X + 1))$                                                                      |

|----------------------|----------------------------------------------------------------------------------------------|

| Solving for X:       |                                                                                              |

| X<br>X<br>X          | = ((FOSC / Desired Baud Rate) / 64) - 1<br>= ((16000000 / 9600) / 64) - 1<br>= [25.042] = 25 |

| Calculated Baud Rate | = 16000000 / (64 (25 + 1))<br>= 9615                                                         |

| Error                | = (Calculated Baud Rate – Desired Baud Rate) Desired Baud Rate                               |

|                      | = (9615 - 9600) / 9600<br>= 0.16%                                                            |

#### TABLE 16-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = Fosc/(4(X+1))   | N/A                        |

Legend: X = value in SPBRG (0 to 255)

#### TABLE 16-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name  | Bit 7   | Bit 6     | Bit 5      | Bit 4                  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |  |

|-------|---------|-----------|------------|------------------------|-------|-------|-------|-------|----------------------|---------------------------------|--|

| TXSTA | CSRC    | TX9       | TXEN       | SYNC                   | _     | BRGH  | TRMT  | TX9D  | 0000 -010            | 0000 -010                       |  |

| RCSTA | SPEN    | RX9       | SREN       | CREN ADDEN FERR OERR F |       |       |       | RX9D  | 0000 -00x            | 0000 -00x                       |  |

| SPBRG | Baud Ra | te Genera | ator Regis | ster                   |       |       |       |       | 0000 0000            | 0000 0000                       |  |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used by the BRG.

TABLE 16-3: BAUD RATES FOR SYNCHRONOUS MODE

| BAUD           | Fosc = | 40 MHz     | SPBRG              | 33 1   | ИНz        | SPBRG              | 25 [   | ИНz        | SPBRG              | 20 1   | MHz        | SPBRG              |

|----------------|--------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|

| RATE<br>(Kbps) | KBAUD  | %<br>ERROR | value<br>(decimal) |

| 0.3            | NA     | -          | -                  |

| 1.2            | NA     | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA     | -          |                    |

| 2.4            | NA     | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA     | -          |                    |

| 9.6            | NA     | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA     | -          |                    |

| 19.2           | NA     | -          | -                  |